Continued from < Part 1 <

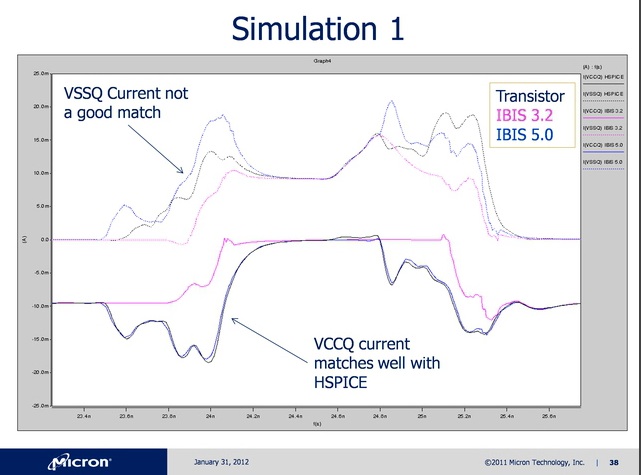

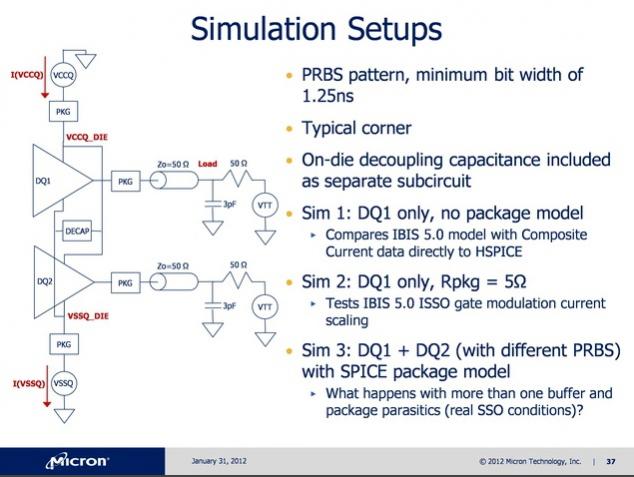

The IBS 5.0 model shows good correlation to full HSPICE simulations on simulation 1 (ISSQ is not accurate enough, yet but IDDQ is.)

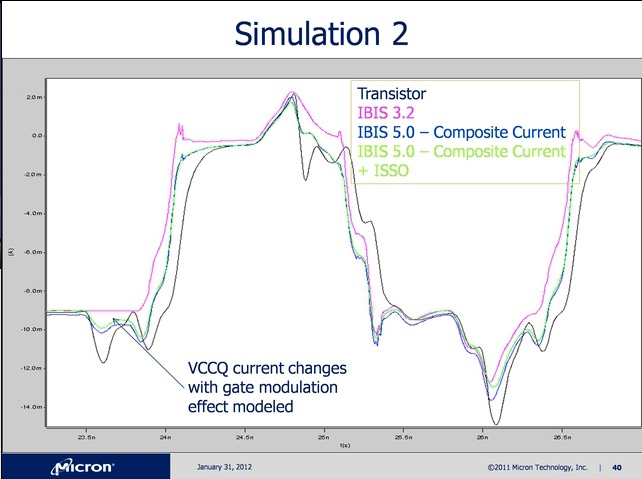

A simple package model with resistance shows good correlation again between IBIS5.0 models and HSPICE:

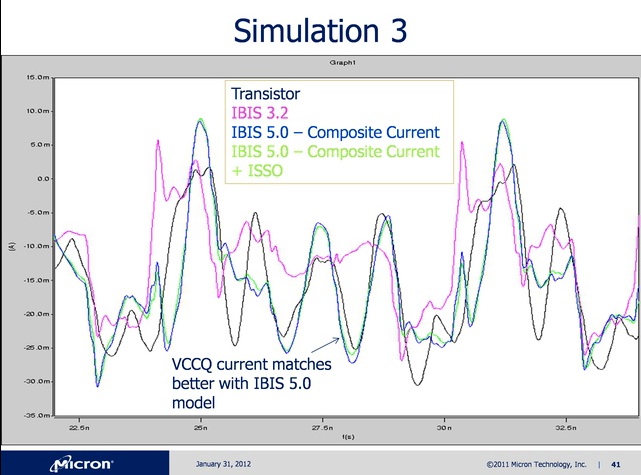

Results from Simultaneous Switching Outputs (SSO) shows how good IBIS5.0 models are compared to HSPICE results:

- IBIS5.0 is ready and simulates well in HSPICE 2011.09 for Power Integrity simulations

- Composite Current data adds more accuracy

- IBIS5.0 simulation on case #3 was 1.6 seconds versus HSPICE full transistor-level at 290.6 seconds, speedy and accurate

- Use IBIS5.0 you’ll like it

[TABLE] cellpadding=”3″ cellspacing=”3″ style=”width: 700px”

|-

| valign=”top” |

| valign=”top” | Scott Wedge

Sr. Staff Engineer

Synopsys

HSPICE for Signal Integrity—A Peek Under the Hood

|-

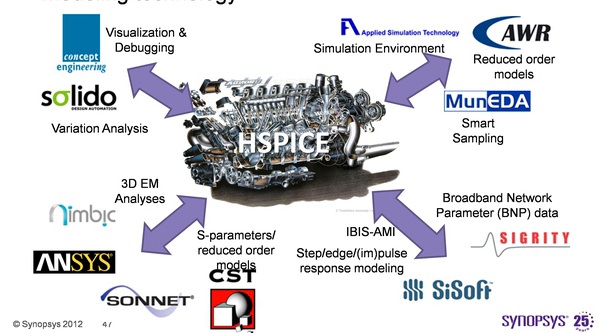

We enjoy partnering with many vendors based on HSPICE simulation and modeling technology:

You can use HSPICE for Signal Integrity tasks, like:

- Transient Analysis

- Network Parameter Analysis

- AC Analysis

- Statistical Eye Diagrams

- Transient Noise

- Frequency-dependent elements in time domain simulation

How to run faster? Using parallelism with multi-threaded simulation: 10X faster on 16 cores. Product is called HSPICE Precision Parallel Technology.

You can also model scattering parameters in HSPICE using the S-element. Works with parallel simulation too.

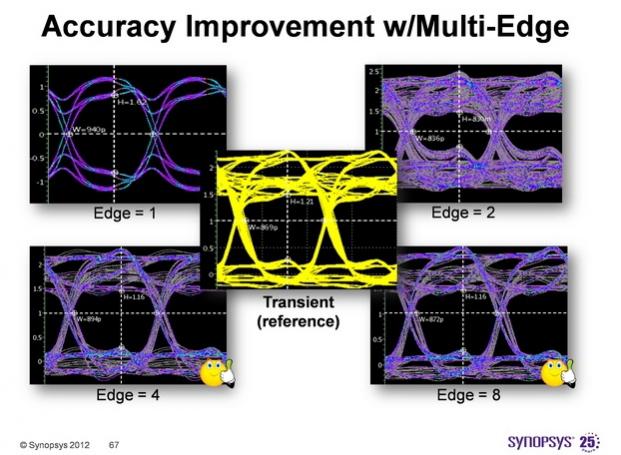

Speeding up slow transient runs for eye diagram analysis is what we call HSPICE StatEye to calculate Bit Error Rate (BER).

HSPICE does support IBIS-AMI models using StatEye.

How to eliminate eye closure (crosstalk, random jitter, duty cycle distortion, periodic jitter)? Simulate with pattern specific inputs and fast transient, use 8b/10b encoding, add pre-emphasis and de-emphasis, try IBIS-AMI models.

Multi-edge support in StatEye will extend capabilities in capturing non-linearities.

- HSPICE plays well with multiple EDA point tools.

- HSPICE StatEye speeds up eye diagram analysis.

My Take

HSPICE has grown from Hailey brothers at Meta-Software, survived the Avant! acquisition, transitioned into Synopsys and continues to be relevant today against a crowded field of competitors. Now with the acquisition of Magma and their FineSim SPICE circuit simulator I’m very curious to see what the product roadmap will look like for circuit simulators both at the SPICE and FastSPICE ends of the spectrum.

Comments

0 Replies to “HSPICE Users Talking about Their Circuit Simulation Experience, Part 2”

You must register or log in to view/post comments.