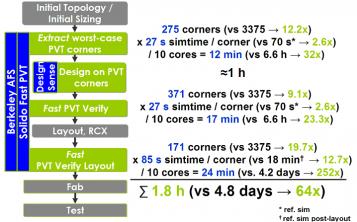

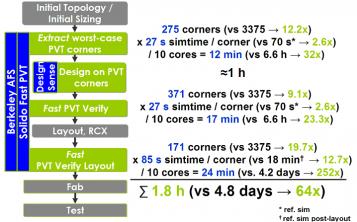

On Sept 22, 2011, the nm Circuit Verification Forumwill be held in Silicon Valley, hosted by Berkeley Design Automation. At this forum, Trent McConaghy of Solido DA will present a case study on the TSMC Reference Flow 2.0 VCO circuit, to showcase Fast PVT in the steps of extracting PVT corners, verifying PVT, and doing post-layout PVT verification. The presentation will cover the speed benefit of Solido Fast PVT, and the multiplicative speed benefit when combined with Berkeley DA’s Analog FastSpice simulator. The picture below shows the benefits in the context of a corner-driven design flow, reducing the time taken for a thorough PVT flow from 4.8 days to 1.8 hours.

Process, voltage, and temperature (PVT) variations are often modeled as a set of PVT corners. Traditionally, only a handful of corners have been necessary: with FF and SS process (P) corners, plus extreme values for voltage (V) and temperature (T), all combinations would mean 2^3=8 possible corners.

With modern processes, many more process corners are often needed in order to properly bracket process variation across different device types. Furthermore, transistors are smaller, performance margins are smaller, voltages are lower, and there may be multiple supply voltages. To properly bracket these variations, more variables with more values per variable are needed.

This leads to more corners. Consider the reference VCO circuit from the TSMC AMS Reference Flow 2.0 on the TSMC 28nm process. A reasonable setup of its PVT variation has 15 modelset values, 3 values for temperature, and 5 values for each of its three voltage variables, totalling 3375 corners. Industry-standard simulators take 70 s to simulate this, which means it takes 66 hours to evaluate all corners. Even with 10 parallel cores, runtime is 6.6 hours.

Designers may cope by guessing which corners cause the worst-case performance, but that is risky: a wrong guess could mean that the design hasn’t accounted for the true worst-case, which means failure in testing followed by a re-spin, or worse, failure in the field.

And what about layout parasitics? Ideally one does a thorough PVT analysis after layout. But each of these simulations takes 18 minutes on industry-standard simulators. Therefore, even with 10 cores, it would take 4.2 days to run 3375 corners.

What is sorely needed is a way to quickly yet thoroughly identify worst-case PVT corners, when there are hundreds, thousands, or even tens of thousands of possible corners.

Solido Design Automation has developed a new application called Fast PVT to address this. It uses adaptive machine learning technologies to rapidly identify the worst-case corners, often reducing the number of simulations by 10x or more. Fast PVT enables users to rapidly extract a handful of worst-case corners, which the user subsequently uses in rapid-turnaround design iterations. Once the corners meet spec, Fast PVT can be used for a more conservative PVT verification. Fast PVT is also applicable to post-layout analysis.

Of course, PVT is not always the way. Some designers have access to sufficiently good statistical MOS models to consider doing statistical analysis, which is inherently more accurate than PVT. Ideally, one would consider statistical process variation effects during the design loop, in order to get to optimal power, performance, and area subject to a target yield. However, since Monte Carlo (MC) simulations are far too slow within the design loop, MC is traditionally run as a verification afterthought. For high-sigma, the challenge is even greater, since it is not feasible to do the 5 billion or so MC simulations to verify at 6 sigma yield. There is a final challenge: designers don’t traditionally think in statistics, they think in terms of corners.

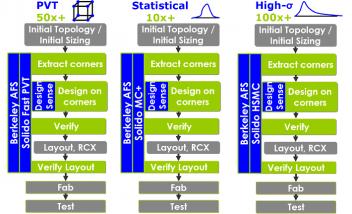

Fortunately, there is a way for designers to design with corners, yet consider statistical (and even high-sigma statistical) variations. The key is to extract statistical corners that actually bound the 3-sigma or 6-sigma output performance for the design at hand. To reiterate: these corners bound the performance of the circuit in a statistical sense, rather than traditional global MOS models like “FF” which bound the performance of the device. Also, there needs to be a fast, pragmatic statistical (or high-sigma statistical) verification step. These steps of corner extraction and verification incorporate into a familiar-feeling corner-driven design flow: extract corners, design against them, then verify, and iterate if needed.

This is exactly the same flow as the PVT corner-driven flow. The only difference is how corner-extraction / verification tools themselves behave. In the end, we have a unified, designer-friendly approach to handle PVT, statistical, or high-sigma variation.

As shown below, Solido DA supplies appropriate tools to support the flows for all three styles of variation, and in conjunction with Berkeley DA’s AFS, provides speedups of 10x+ to 100x+.

Trent McConaghy is the Solido Chief Science Officer, an engaging speaker, and someone who I have thoroughly enjoyed working with the past two years. If you are doing 28nm analog/RF, IO, memory or standard cell digital library design you will not want to miss talking to Trent!

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.