The design of an SRAM array requires focus on the key characteristics of readability, writeability, and read stability. As technology scaling has enabled the integration of large (cache) arrays on die, the sheer number of bitcells has necessitated a verification methodology that focuses on “statistical high-sigma” variation analysis. Designers must ensure that the statistical number of “weak cells” that may fail the characteristics above is sufficiently low, and adequately covered by the array’s architecture for error detection/correction and redundant rows and columns.

The design of an SRAM array requires focus on the key characteristics of readability, writeability, and read stability. As technology scaling has enabled the integration of large (cache) arrays on die, the sheer number of bitcells has necessitated a verification methodology that focuses on “statistical high-sigma” variation analysis. Designers must ensure that the statistical number of “weak cells” that may fail the characteristics above is sufficiently low, and adequately covered by the array’s architecture for error detection/correction and redundant rows and columns.

The importance of array design robustness is amplified by the goal to operate the array at a unique, often dynamically-adjusted, supply voltage domain, to reduce (active and standby leakage) power.

The “brute force” method to determine the high-sigma SRAM yield subject to PVT variation is to execute a Monte Carlo-based sampling of parameters from their statistical distributions, and simulate circuit behavior with these parameter values. Yet, a suitable assessment of the array yield for a large SRAM requires an inordinate number of Monte Carlo sampled simulations. Algorithms for optimized sampling and circuit response sensitivity to determine high-sigma SRAM yield have been developed, to allow faster array design closure.

One of the leading EDA companies providing optimized variation analysis tools is Solido Design Automation. I recently had the opportunity to chat with Kris Breen, VP of Customer Applications, and Amit Gupta, President and CEO at Solido, about the latest advancements incorporated into the recent Version 4 release of their Variation Designer software. As Kris noted, “At Solido, we are variation specialists — it is our sole focus. We recognize that high-sigma yield analysis requires unique expertise. We assist customers with extensive education offerings and best practices methodology support.” (as an integral part of product licensing). Solido has clearly identified an important area in IC design — their year-over-year revenue growth in 2015 was 70%, in an otherwise tepid EDA market.

Before delving into the latest capabilities of Variation Designer for SRAM analysis, here’s a little background on this crucial SoC design topic.

As mentioned above, the anticipated “yield” of an SRAM array dictates the architectural decisions (e.g., redundancy) and performance/power tradeoffs (e.g., a unique VDD supply domain, with operating and standby modes). The volume of bitcells requires a “high-sigma” yield analysis, while the extensive die area allocated to large arrays requires attention to global and local parameter variation.

SRAM yield analysis basics

SRAM bit cell circuit analysis involves simulation of three main characteristics:

Read stability (RS)

Read stability implies that the cell stored value is unaffected by switching activity in the surrounding neighborhood. Further, a read access to the cell, and the corresponding read current between cell and bitlines, does not result in a sufficient internal node voltage drop to potentially “flip” the stored value.

Read access performance (RA)

A read access fail would occur if the driven bitline voltages have not reached a suitable differential at the inputs to the sense amplifier, at the time in the access cycle when the sense amp is enabled. Note that statistical process variation yield analysis involves the bit cells in combination with the sense amplifier sensitivity, as reflected in the design margin required for sense amp offset.

Write access (WA)

During a write cycle, the bitline differential is transferred to the bitcell, with sufficient current to overdrive the existing internal node voltages. A write access failure would result from an insufficient transition within the cell (i.e., to some % of VDD for the ‘1’ node) by the end of the cycle — although the positive feedback within the cell would continue to boost node voltages, an immediate read to the same cell location would need sufficient read current drive, as described above.

All these characteristics must be robust across PVT variations — specifically, at a reduced VDD supply voltage.

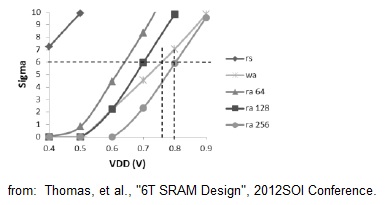

The figure below provides an illustration of how the “sigma yield” of an example array would vary with VDD, for RS, WA, and RA (with RA examples using different numbers of bitcells per column).

Solido’s Variation Designer has traditionally included a High-Sigma Monte Carlo (HSMC) array analysis feature, with specific statistical sampling optimizations to reduce the requisite number of Spice circuit simulations to realize a yield assessment with accurate cases at the tail of the yield distribution (e.g., 6-sigma and greater). The results are not an “extrapolation” of a distribution curve, but provide specific circuit simulation samples at high sigma for further analysis of the selected parameter values. (As process statistical distributions are increasingly non-Gaussian, extrapolation to the high-sigma tail of an overall yield is highly inaccurate.)

Kris highlighted, “Our methodology works seamlessly with our customer’s existing Spice circuit simulation environment. Variation Designer works with all commercial Spice products. If you can measure it, you can use Solido to analyze it.”

Specifically, this release of Variation Designer extends the High-Sigma Monte Carlo feature for SRAM yield analysis, with a new “Hierarchical Monte Carlo” capability. The variation experts at Solido identified an opportunity to improve the accuracy of the SRAM yield methodology — the yield is an intricate interdependence between variations in different functional blocks of the overall array — e.g., bitcell, bitline pre-charge, sense amplifier, address decode, word line drivers.

With a memory slice or critical path and a minimal amount of architectural information as input from the designer, Hierarchical Monte Carlo statistically reconstructs the full on-chip memory to produce accurate full-chip yield results. Hierarchical Monte Carlo works by sampling each component on the slice or critical path with the correct statistical frequency – for example, 3 sigma global statistical variation, 4 sigma on control circuitry, 5 sigma on sense amps, and 6 sigma on bitcells. Runtimes are still fast, as only the slice or critical path is ever simulated in Spice, and because the millions or billions of correctly structured samples are massively reduced using technology similar to Solido’s HSMC such that only thousands of simulations are actually run.

According to Solido, this is the first time the problem of statistically verifying memory critical paths and slices has been accurately solved. Previous methods were pessimistic by 10%-60%, as measured in comparison studies done by Solido’s customers. The advantage of getting the right answer is that it enables designers to tighten margins significantly, producing faster, lower power, memories that are less expensive to produce.

This latest release of Variation Designer also includes updates to allow designers to enhance their analysis to more effectively incorporate process and environment parameters together. Alas, I’m out of space for this article — look for a subsequent article on Variation Designer’s Statistical PVT features soon.

For more information on Solido’s technology, please follow this link.

-chipguy

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.