Improper handling of design validation could simply translate into a debugging exercise. In mainstream RTL2GDS flow, design implementation involves a top-level integration and lower-level block developments. These lower-level components, comprising of macros, IPs and standard cells are subjected to frequent abstraction… Read More

Electronic Design Automation

IP Vendor Tuning of Your SoC A Practice for Design Success

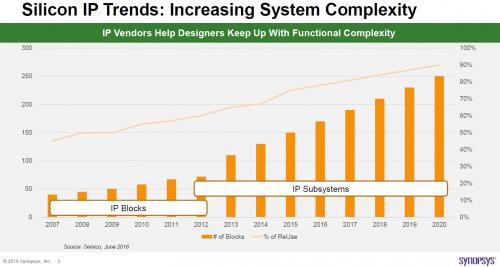

On April 17, Mick Posner, Director of Product Marketing, IP Subsystems, Hardening & IP Kit solutions held a Webinar entitled ‘Getting more from your IP Vendor, IP Tuned to Your SoC’. This brought back memories of the challenges in days past of making the right choices in IP selection, integration and validation when prudence… Read More

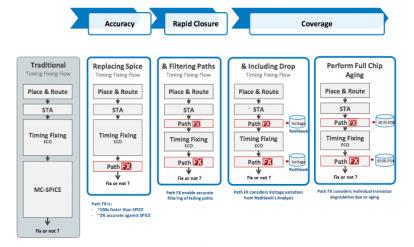

Peering Over the Timing Edge

I wrote recently about a yield problem which mobile vendors have been finding for devices built in advanced technologies. This was a performance issue (the devices worked fine at lower clock speeds), pointing to a discrepancy in some devices between predicted and observed timing. These were experienced design teams, using state… Read More

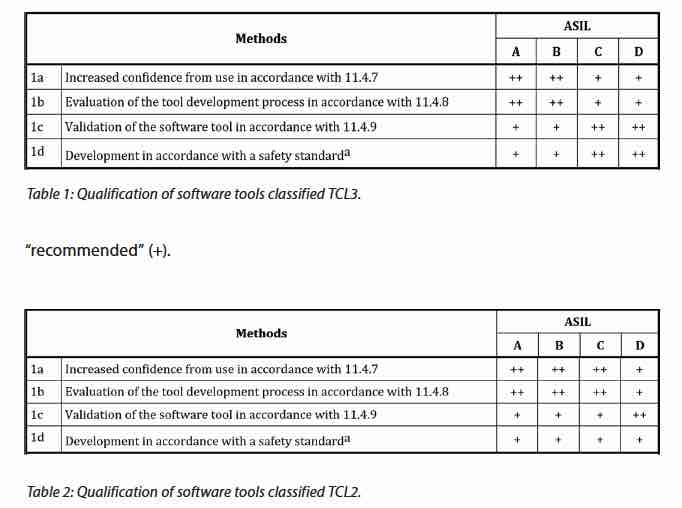

ISO 26262: Automotive electronics safety gets an update in 2018

In the field of automotive electronics, the year 2011 was a long time ago. So, it is about time that the initial ISO 26262 specification that was adopted back then gets an update. The latest version will be known as ISO26262:2018 and will expand the scope of the original to cover more types of vehicles. It will add an entire section on… Read More

2018 Women in Engineering Achievement Award

Having spent my entire thirty plus year career in semiconductors and design enablement I have seen quite a change in diversity. When I first started I remember thinking that height and weight was the only diversity here in Silicon Valley. My wife really noticed it when she attended her first Design Automation Conference in 1985 … Read More

Virtuoso at CDNLive – A Press Briefing With Yuval Shay

At CDNLive Silicon Valley 2018, I talked with Yuval Shay, Director of Product Management of Cadence Custom IC & PCB Group to scope out some more details on the recent Virtuoso product refresh announced earlier in the morning by Cadence Sr. VP & GM of the same group, Tom Beckley.

Tom shared his view on enabling the fourth industrial… Read More

imec and Cadence on 3nm

One of the more frequent questions I get, “What is next after FinFETs?” is finally getting answered. Thankfully I am surrounded by experts in the process technology field including Scotten Jones of IC Knowledge. I am also surrounded by design enablement experts so I really am the man in the middle which brings us to a discussion between… Read More

Monitoring Process, Voltage and Temperature in SoCs, webinar recap

Have you ever wondered how process variation, thermal self-heating and Vdd levels affect the timing and yield of your SoC design? If you’re clock specification calls for 3GHz, while your silicon is only yielding at 2.4GHz, then you have a big problem on your hands. Such are the concerns of many modern day chip designers. To… Read More

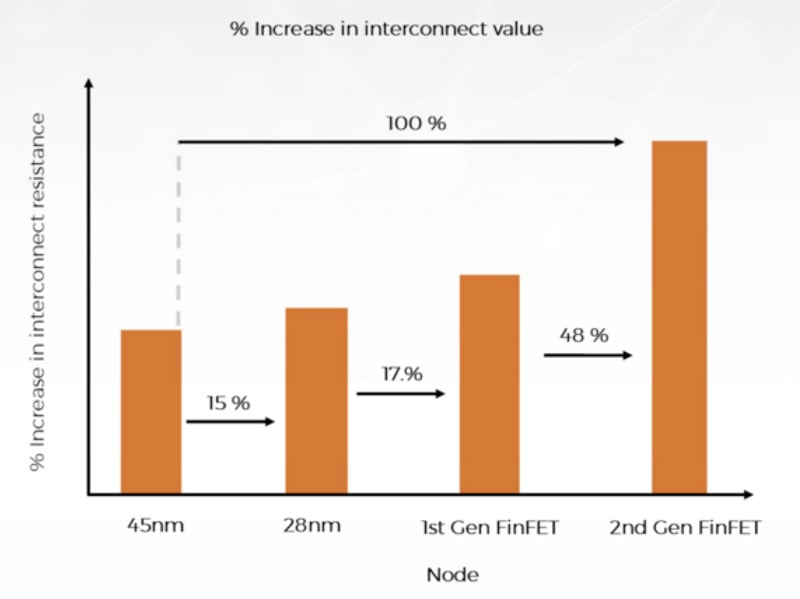

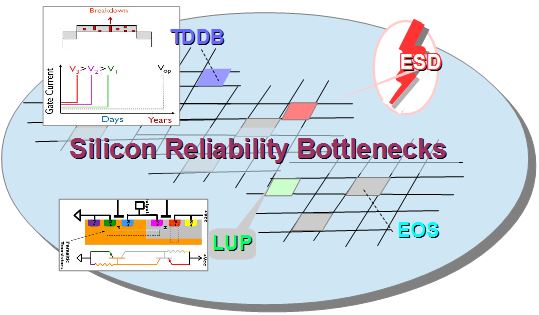

Electrical Reliability Verification – Now At FullChip

Advanced process technology offers both device and interconnect scaling for increased design density and higher performance while invoking also significant implementation complexities. Aside from the performance, power and area (PPA) aspects, designer is getting entrenched with the need of tackling more reliability … Read More

Functional Safety in Delhi Traffic

While at DVCon I talked to Apurva Kalia (VP R&D in the System and Verification group at Cadence). He introduced me to the ultimate benchmark test for self-driving – an autonomous 3-wheeler driving in Delhi traffic. If you’ve never visited India, the traffic there is quite an experience. Vehicles of every type pack the roads … Read More

Solving the EDA tool fragmentation crisis