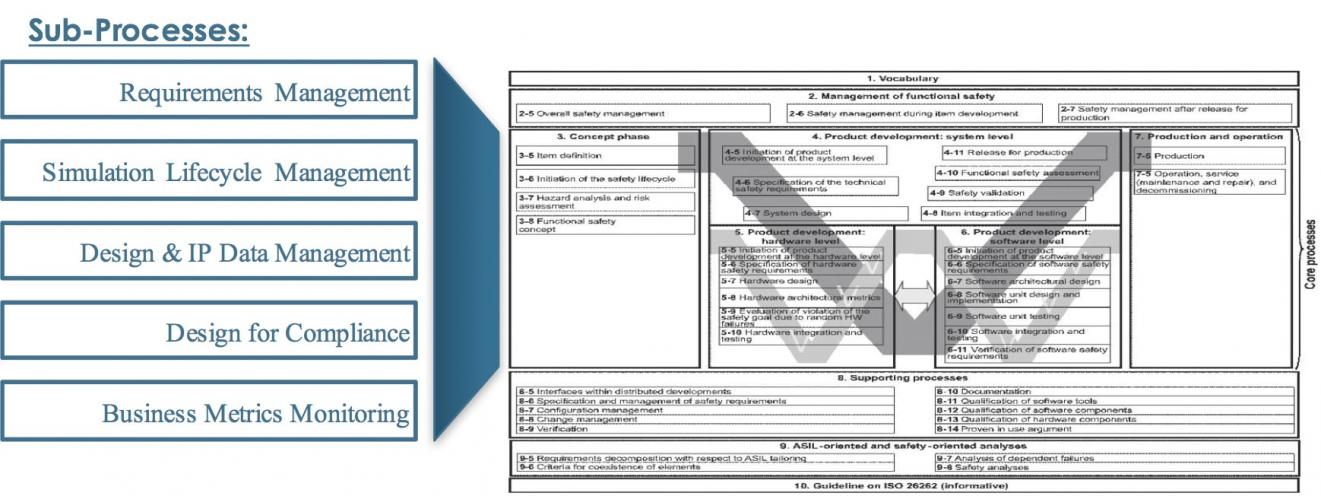

Reading the many articles on SemiWiki and other publications we find experts talking about the automotive market, mostly because it’s in growth mode, has large volumes and vehicles consume more semiconductors every year. OK, that’s on the plus side, but what about functional safety for automotive electronics?… Read More

Electronic Design Automation

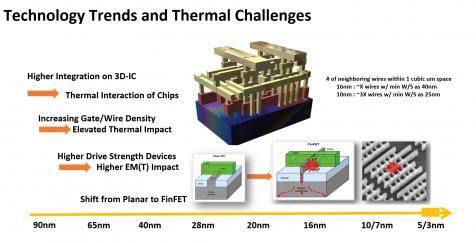

Thermal and Reliability in Automotive

Thermal considerations have always been a concern in electronic systems but to a large extent these could be relatively well partitioned from other concerns. Within a die you analyze for mean and peak temperatures and mitigate with package heat-sinks, options to de-rate the clock, or a variety of other methods. At the system level… Read More

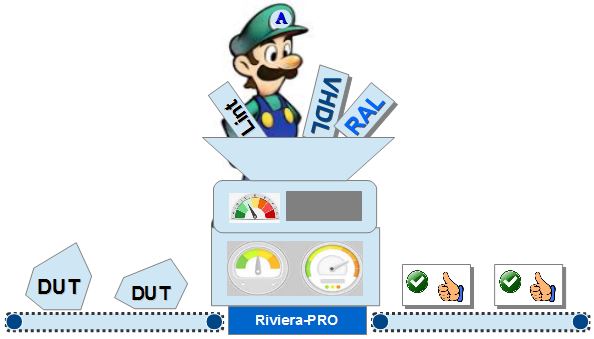

RAL, Lint and VHDL-2018

Functional verification is a very effort intensive and heuristic process which aims at confirming that system functionalities are meeting the given specifications. While pushing cycle-time improvement on the back-end part of this process is closely tied to the compute-box selection (CPU speed, memory capacity, parallelism… Read More

DRC is all About the Runset

EDA companies advertise their physical verification tools, aka DRC (Design Rule Check), mostly in terms of specific engine qualities such as capacity, performance and scalability. But they do not address an equally if not more important aspect: the correctness of the actual design rules.

Put bluntly: It’s not about how… Read More

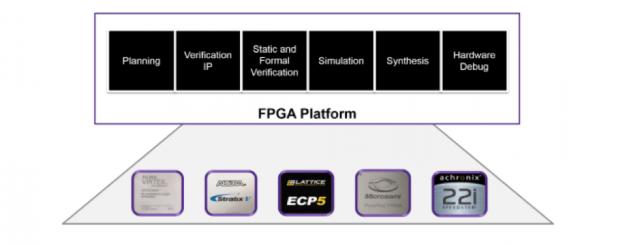

When FPGA Design Looks More Like ASIC Design

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More

John Lee: Market Trends, Raising the Bar on Signoff

I talked to John Lee (GM of the ANSYS Semiconductor BU) recently about his views on market trends and the ANSYS big-picture theme for DAC 2018. He set the stage by saying he really liked Wally’s view on trends (see my blog on Wally’s keynote at U2U). John said these confirm what he is seeing – a trend to specialization, some around… Read More

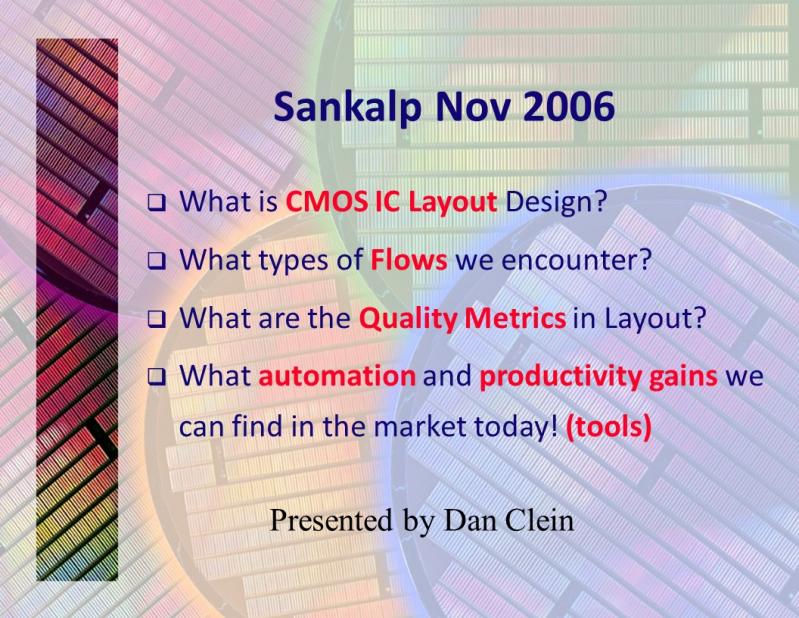

Is there anything in VLSI layout other than “pushing polygons”? (10)

The year is 2005 and PMC Sierra decided that it is time to expand by adding a new site in Bangalore, India. We started with digital verification first but by 2006 we were ready to engage with Mixed Signal Design and Layout. I went to Bangalore in June 2006 for the first time and with the help of our local manager, Vikram Labhe, had a few layout… Read More

Mentor Siemens Update 2018

As you know I am a big fan of disruption and the Siemens acquisition of Mentor is turning out to be one of my favorite EDA disruptions. At first it was a little bit perplexing but after one short year it makes complete sense.

Siemens is acquiring Mentor as part of its Vision 2020 concept to be the Benchmark for the New Industrial Age. It’s… Read More

CEO Interview: Jason Oberg of Tortuga Logic

I first met Jason Oberg, CEO and one of the co-founders of Tortuga Logic, several years ago when I was still at Atrenta. At that time Jason and Jonny Valamehr (also a co-founder and the COO) were looking for partners. The timing wasn’t right, but we’ve stayed in touch, for my part because their area of focus (security) is hot and likely… Read More

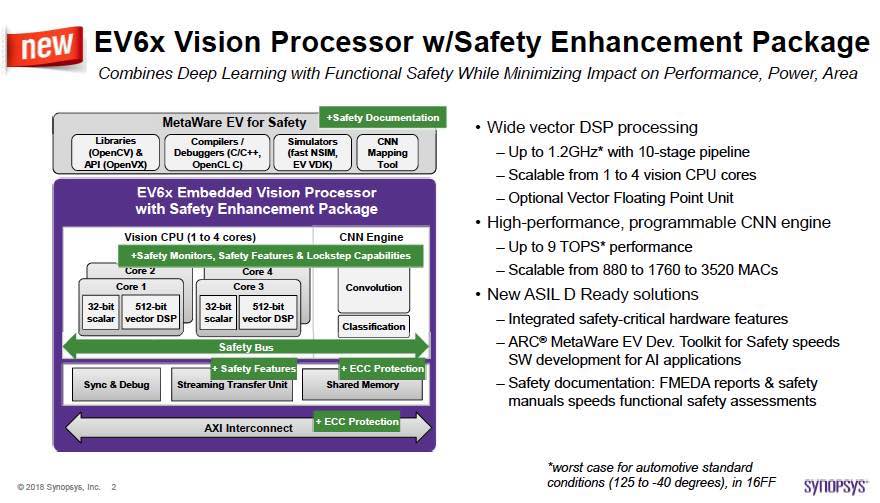

ISO 26262 First – ASIL-D Ready Vision Processor IP Available

Synopsys made a pretty major announcement regarding their new ASIL-B,C and D ready embedded vision processor IP. This matters because you cannot bolt on the design elements and features needed to achieve these ASIL levels later, and this IP is absolutely necessary for ADAS systems and other critical safety systems in automobiles.… Read More

Solving the EDA tool fragmentation crisis