IC designers contemplating the transition to 16nm FinFET technology for their next SoC need to be informed about design flow and IP changes, so TSMC teamed up with Cadence Design Systems today to present a webinar on that topic. I attended the webinar and will summarize my findings.

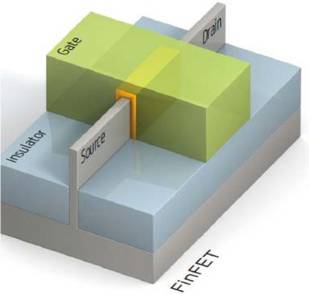

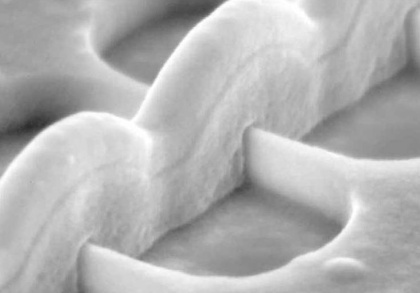

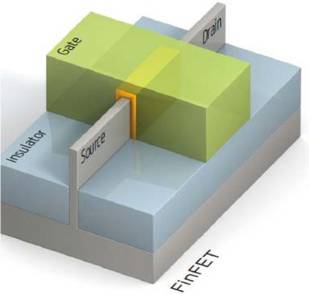

Shown below is a 3D layout concept of an ideal FinFET transistor, followed by the actual manufactured device which is rotated 90 degrees from the layout:

Brian Fuller from Cadence hosted the webinar and talked about how they’ve worked with TSMC over the past 12 months to certify a new tool flow specifically aimed at the 16nm node.

Jason ST Chen, Design Methodology & Service Marketing for TSMC led off with the benefits of FinFET: lower leakage, lower power, and higher drive currents. There are however several new challenges with FinFET design that need to be addressed:

- Device Width is quantized – so Place and Route, plus custom design tools need updates

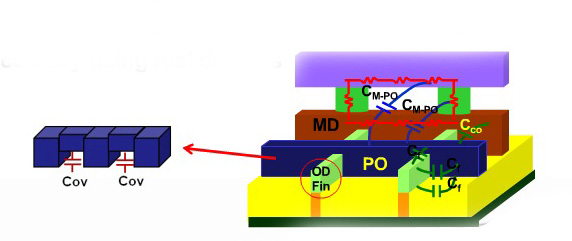

- 3D structure -requires 3D RC extraction

- Increased gate capacitance – impacts Static Timing Analysis (STA)

- Stronger Miller Effects – requires certification of Electro-migration (EM), IR and STA tools

The 16nm FinFET process compared to 20nm at TSMC provides about a 20% performance improvement at the same power, or a 40% power savings at the same performance, while the gate density is the same.

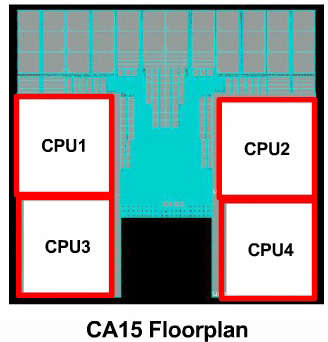

An SoC with the ARM Cortex-A15 CPU has been designed and pushed through the new tool flow at Cadence to ensure that everything works properly between foundry, IP and EDA vendor tools.

The Automatic Place and Route (APR) tool has to enforce the new FinFET placement-based rules, while ensuring that pin access to cells follows more difficult standards.

STA results have to be correlated with SPICE results in order to keep accuracy in bounds.

With 3D layout also comes 3D extraction, often requiring a 3D field solver on critical cells.

At 16nm the potential for EM and IR drop failure increases, so additional analysis is required. These EM and IR results are then correlated to SPICE for accuracy, while enabling faster analysis times.

SPICE is often used as the golden reference for timing, current and power measurements, so TSMC has to qualify a vendor’s SPICE circuit simulator for accuracy.

Analog circuits were also validated in the TSMC 16nm process using a PLL and VDAC IP blocks in a tool flow that was:

- Parasitic-aware

- Layout Dependent Effect (LDE) aware

- Voltage Dependent Rule Check (VDRC)

- EM/IR compliant

- RC extraction for 3D structures

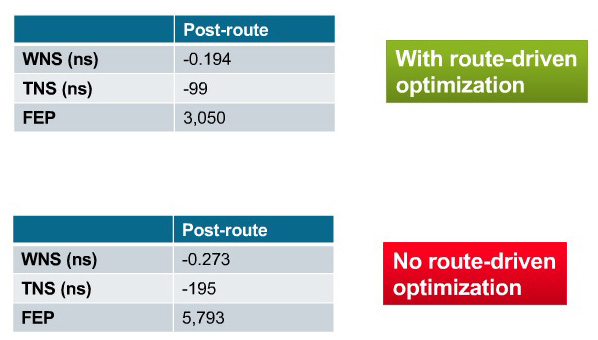

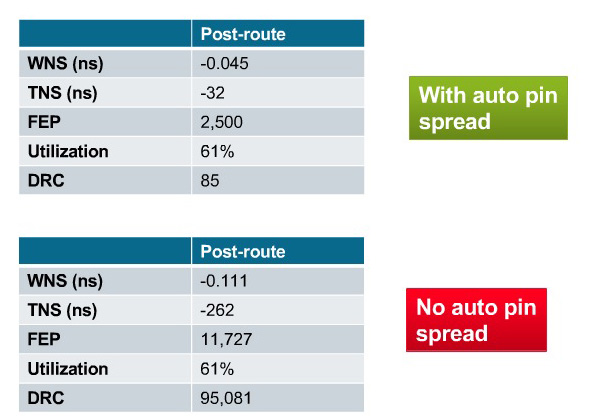

Up second, after TSMC was Paddy Mamtora of Cadence to talk about using P&R with the Encounter tool. Resistance impacts timing closure, and at 16nm the design rule complexity has again increased over 20nm, causing more strains on P&R tools. He shared how their new APR approach uses route-driven optimization, and had some data from the CA15 test chip where the worst negative slack (WNS) numbers improved:

Pin access has become more difficult at 16nm so a new auto-pin spread feature was added to Encounter, once again improving timing and DRC closure results:

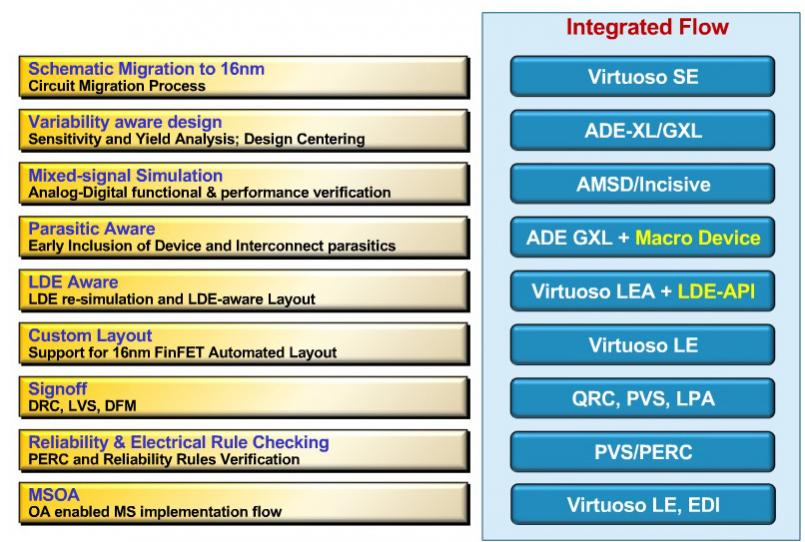

Mladen Nizic from Cadence presented on how the custom design flow had been improved to deal with 16nm FinFET challenges. This next diagram shows the custom design tasks on the left and specific EDA tools on the right that have been upgraded:

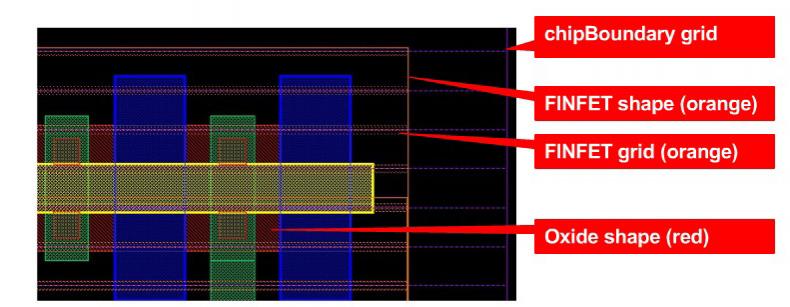

An AMS reference design has an LPF amplifier and fractional-N type PLL. Custom design layout requires that the layout design see a fin-grid display, and use automation for snapping to grids.

More custom design automation is provided by device module generators (ModGen), so they are 16nm ready and save time by creating layouts that are correct-by-construction.

Starting with the 20nm node the need for Double Pattern Technology (DPT) was introduced and it continues at the 16nm node. DPT coloring can be automated by using the latest Virtuoso tools.

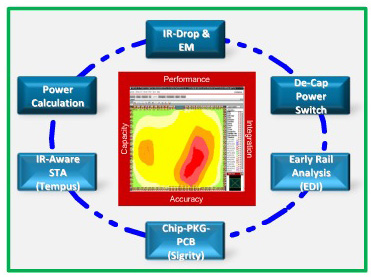

The final Cadence speaker was Ruben Molina and he explained the importance of silicon sign-off and verification.

At Cadence their SPICE circuit simulator is called Spectre, and they have a new version called Spectre XPS that is about 10X faster than Spectre while using up to 3X less RAM. With all of the Monte-Carlo simulations to account for process variation, having a faster SPICE simulator really helps get the job done in a reasonable amount of time while maintaining accuracy.

For 3D extraction Cadence has a tool called QRC and it can use a 3D field solver for the most sensitive circuits. QRC is qualified in the TSMC flow.

The new STA tool at Cadence was launched last year, and it’s named Tempus. Timing analysis is speeded up by a parallel architecture and it’s 16nm ready.

On the power analysis side, the Cadence tool name it Voltus, also launched last year. Analysis in Voltus is massively parallel, and has the capacity for full-chip analysis.

Competing directly with Mentor’s Calibre tools for DRC and LVS is the Cadence Physical Verification System (PVS) that has the capacity to handle 16nm designs along with their greatly increased number of rules.

Summary

With just 60 minutes of time scheduled for this webinar, there was enough information presented to have another hour of questions, however for the sake of time the Q&A session was handled offline. It’s clear that foundry, IP and EDA vendors were required to all work together in parallel as the 16nm node was defined and developed. Every new challenge has been met at 16nm, and now the only big question is one of economics for your particular SoC and how it may benefit from a faster design or lower power design compared to 20nm.

lang: en_US

Share this post via:

Comments

0 Replies to “Designing an SoC with 16nm FinFET”

You must register or log in to view/post comments.