Cadence invests heavily in the development of their Tempus Timing Signoff Solution due to its importance in the SoC design flow. I recently had a discussion on the topic of the most recent Tempus update with Brandon Bautz, senior product management group director in the Digital & Signoff Group, and Hitendra Divecha, product management director in the Digital & Signoff Group. They updated me on the goals and contents of their latest software release. Cadence’s main goal was to remove time-to-market bottlenecks while enabling designers to achieve best-in-class power, performance and area (PPA). To achieve this, their software release focused on easing advanced-node design complexity and model challenges while continuing to improve designer productivity.

Design complexity growth has been extremely fast at advanced nodes. Significant increases in design size and signoff corners plus the emergence of advanced packaging methodology like 3D-IC have driven an exponential increase in design complexity at advanced nodes. At the same time, many new types of analyses are needed, and existing analyses have become more in-depth. For example, at advanced nodes, process and voltage variation become significantly more challenging to analyze. Also, designers are more concerned about design performance at ultra-low Vdd operating ranges. Designers are stressed because there are more iterations, time-to-market windows are shrinking, signoff complexity is increasing and there are tighter performance specs, including low power, high reliability and robustness.

The Cadence product management team had to pick their customers’ highest impact avenues to take on all of the above factors and improve time to market for designs with the best PPA. Interestingly, much of their customer focus has been on what you might call human factors. Two of their focus areas are usability/ease of use and world-class support. They also set out to reduce the total number of iterations from synthesis to signoff. Last, but not least, they knew they had to provide optimization and PPA that was best in class.

How did they go about this with Tempus 21.1? There are five main elements on their list of what’s new.

Tempus SmartMMMC Optimization is the first of these and handles multi-mode multi-corner (MMMC) concurrent optimization. In their timing closure nomenclature, a view is a specific corner combined with a specific mode. Present-day SoCs often call for analysis of more than 200 views. Without a fast and effective method to perform this analysis, designers must manually prune the number of views in an attempt to save time. SmartMMMC optimization automatically performs view compaction to eliminate redundant analysis. This reduces memory requirements and turnaround time, while maintaining PPA.

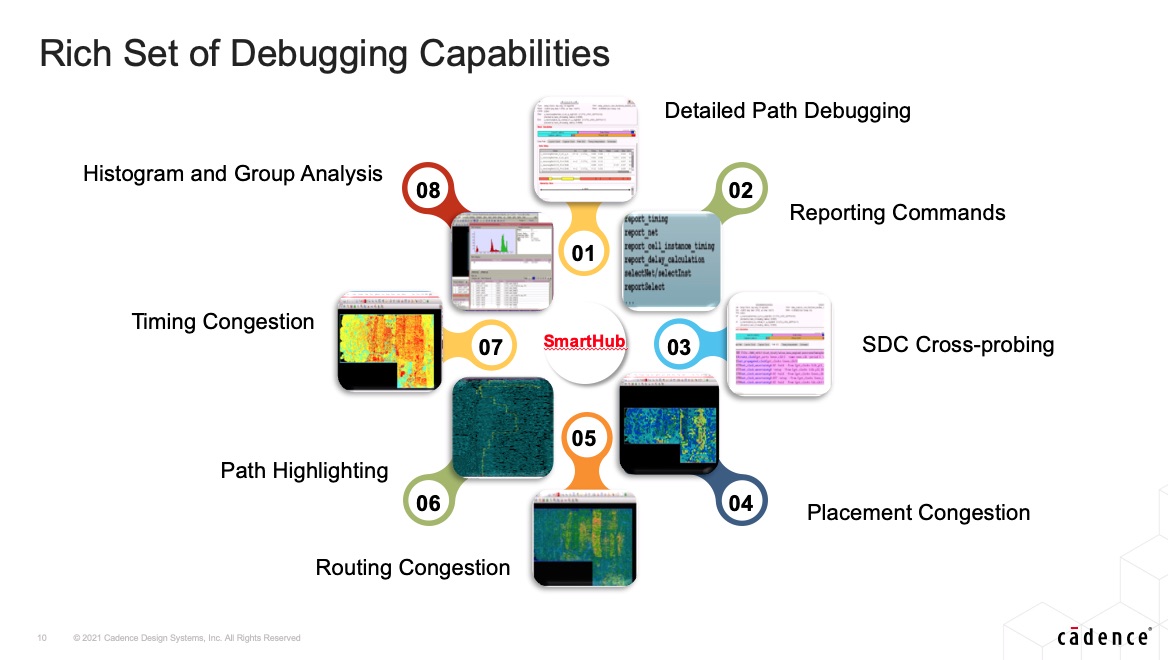

For “last-mile” ECOs, Tempus SmartHub provides an environment for making manual ECOs that does not throw the design back into the full design iteration process. It provides sufficient flexibility to reach timing closure with signoff criteria at the end of the process. Hitendra said that users can expect to see a 2X faster time to closure using this approach. In fact, it provides a rich set of debugging capabilities, such as timing congestion, path highlighting, routing congestion, SDC cross probing, reports and detailed path debugging.

To address high-capacity signoff closure, the ParaDime flow features full flat timing analysis with top-level context for block-level changes. What makes this even more powerful is that separate users can independently work on their own parts of the design, including portions of the top level to make changes at the same time. Users can specify specific blocks, partitions or even path groups to optimize within their session. ECOs are implemented hierarchically and verified with final flat timing analysis. It easily makes up for it with dramatically improved runtimes and reduced execution memory.

Inter-Power Domain (IPD) is the Cadence approach to reducing the complexity associated with timing analysis at switchable power domain crossings. IPD is able to look at just the logic associated with the domain crossing interface instead of performing multiple full-chip analyses to verify timing performance. Each power domain crossing introduces new combinations of views to cover all voltage combinations. IPD isolates and analyzes only the affected logic to provide complete timing analysis.

Lastly, Hitendra talked about design robustness. This is a set of design methods that result in higher quality designs. Under this umbrella, they include timing robustness, aging-aware STA and voltage robustness. All analysis supports timing-aware and robustness closure in the Tempus ECO Option.

With the timing robustness feature, timing robustness can be added as a cost function so that timing and robustness are both simultaneously optimized. Hitendra said that it is possible to take a 3-sigma design and improve timing robustness optimization and at the same time avoid big power and area penalties. The net effect is a more robust design with minimal negative impacts. Additionally, their timing robustness feature can be used to give 3-sigma design robustness figures that are similar to a 4-sigma design without the power and area costs associated with going to 4-sigma.

Cadence is also looking to handle aging analysis with their aging-aware STA. It will be possible to add instance-specific aging information for STA. They also are simplifying the characterization of the libraries for aging stress profiles. Hitendra pointed out that they are doing this because simple de-rates or fixed-age libs are pessimistic at best.

Finally, the last part of the robustness umbrella is about providing power integrity inputs to the timing closure flow. To do this, Cadence has integrated the Tempus solution and the Voltus IC Power Integrity Solution to create Tempus Power Integrity (PI). Because voltage-sensitive paths are not always timing-critical paths, the tool identifies voltage-sensitive paths and the associated power aggressors based on proximity, electrical connectivity and timing windows. To do this, they need to look at resistance, power, IR drop and timing data. Once weaknesses have been identified, the Tempus ECO Option is used to fix any violations.

Overall, there is a lot to unpack in this significant release of the Tempus solution. Brandon and Hitendra barely managed to cover all the details in our hour-long discussion. However, if you look at the big problem areas that designers are facing today and where Cadence has invested in improving the flow for better results, it’s clear that there is a large overlap. Brandon and Hitendra seemed acutely aware of the issues their customers need to address. SoC design complexity is a moving target, but close attention to technology and customer requirements seems to make all the difference in the ability to deliver valuable solutions. More information at available on the Cadence website.

Also Read

Cerebrus, the ML-based Intelligent Chip Explorer from Cadence

Instrumenting Post-Silicon Validation. Innovation in Verification

EDA Flows for 3D Die Integration

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.