Static Timing Analysis (STA) has been an EDA tool category for many years now, yet with each new generation of smaller foundry process nodes come new physical effects that impact timing, requiring new analysis features to be added. For advanced process nodes, there are five different types of analysis that must be included when… Read More

Tag: tempus

Design Planning and Optimization for 3D and 2.5D Packaging

Introduction

Frequent SemiWiki readers are aware of the growing significance of heterogeneous multi-die packaging technologies, offering a unique opportunity to optimize system-level architectures and implementations. The system performance, power dissipation, and area/volume (PPA/V) characteristics of a multi-die… Read More

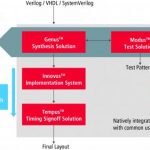

Cadence Tempus Update Promises to Transform Timing Signoff User Experience

Cadence invests heavily in the development of their Tempus Timing Signoff Solution due to its importance in the SoC design flow. I recently had a discussion on the topic of the most recent Tempus update with Brandon Bautz, senior product management group director in the Digital & Signoff Group, and Hitendra Divecha, product… Read More

A True Signoff for 7nm and Beyond

The Tale of Three Metrics

Meeting PPA (Performance, Power and Area) target is key to a successful design tapeout. These mainstream QoR (Quality of Results) metrics are rather empirical yet inter-correlated and have been expanded to be linked with other metrics such as yield, cost and reliability. While the recent CPU performance… Read More

IoT Designs Beginning to Shift to 7nm: Promises Upside for Cadence Physically-Aware Design Flow

Until recently, ICs at bleeding edge nodes like 7nm technology from foundries like TSMC were mostly targeted for high-performance-computing (HPC) and mobile applications or possibly high radix switches that needed the increased performance of advanced nodes. The momentum of Moore’s law and Moore-than-Moore saw foundries… Read More

Cadence’s Tempus – New Hierarchical Approach for Static Timing Analysis

While at the 54[SUP]th[/SUP] Design Automation Conference (DAC) I had the opportunity to talk with Ruben Molina, Product Management Director for Cadence’s Tempus static timing analysis (STA) tool. This was a good review of how the state-of-the-art for STA has evolved over the last couple decades. While the basic problem hasn’t… Read More

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

Innovus: Cadence’s Next Generation Implementation System

Yesterday was the first day of CDNLive. There were three keynotes. The first was by Lip-Bu Tan, Cadence’s CEO (and the Chairman of Walden International that he will be the first to remind you). The most interesting tidbit was that Cadence now has over 1000 people working on IP and that it represents 11% of their revenue. Then… Read More

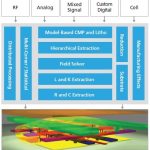

A Deeper Insight into Quantus QRC Extraction Solution

Last month Cadenceannounced its fastest parasitic extraction tool (minimum 5 times better performance compared to other available tools) which can handle growing design sizes with interconnect explosion, number of parasitics and complexities at advanced process nodes including FinFETs, without impacting accuracy of … Read More

Signoff Accurate Timing Analysis at Improved Run-time & Capacity

The semiconductor design sizes, these days, can easily be of the order of several hundred millions of cells, adding into the complexity of verification. Amid ever growing design sizes, it’s a must that the timing verification is done accurately. Normally Static Timing Analysis (STA) is done to check whether all clocks and signals… Read More