Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making it almost impossible to validate the whole system by traditional means. In such a scenario, nothing can be better than having a complete platform which enables designers to connect these components together at various abstraction levels (even before their RTL level implementation), optimize their architecture in terms of power and performance, validate the whole system and present a prototype that can lead the actual implementation without much problems, thus significantly improving the total turn-around-time of the system development.

It was a pleasant surprise coming across Vista Virtual Prototyping solution which is part of the Vista[SUP]TM[/SUP] Platformof Mentor Graphics. I read Mentor’s whitepaper, “Vista Virtual Prototyping” with rapt attention as it gives interestingly good level of details about the working of the system and how it can solve the big problem of optimizing (power and performance) and deciding about the overall architecture of the system. I am summarising some of those points below, but would recommend the audience to read the paper to know about the actual details; it’s an interesting and engaging read.

Primarily the system has two main parts – i) TLM (Transaction Level Modelling) based platform for creation of models for Virtual Prototype, ii) Platform to use the Virtual Prototype, integrate and validate software and firmware on the whole system. Here are some of the important and easy-to-use components of the platform –

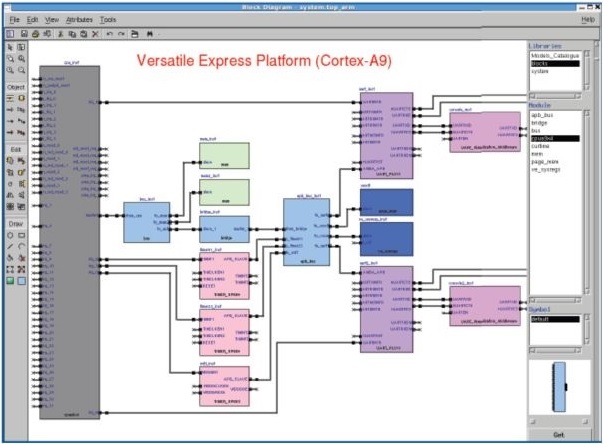

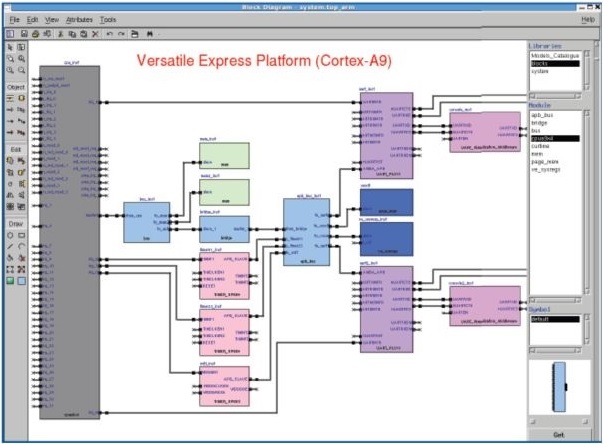

[Vista Schematic Block Diagram Editor]

The block diagram editor provides a simple schematic creation by linking graphic symbols of various TLM models. It’s possible to view and modify the SystemC source code of any TLM instance. On each save operation, the structural SystemC code of the schematic view is automatically generated and saved.

After design phase of the Virtual Prototype, it can be used by software and firmware engineers for software development as well as several verification tasks such as HW/SW analysis, HW/SW co-simulation and debugging. It supports UI, application stacks, firmware and drivers running on top of OS such as Linux, Android and Nucleus as well as Bare-Metal mode. And it provides facilities to develop Linux kernels and fast booting of the OS. It can also be linked with physical devices of the host workstation such as terminals, displays, USBs, Ethernet connections etc.

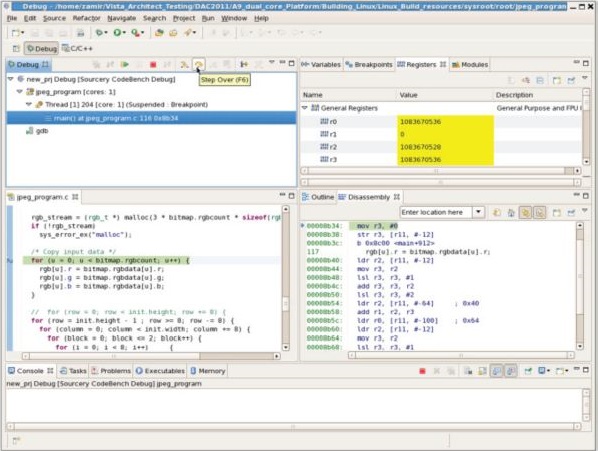

Although Vista Virtual Prototype can be invoked from the command line, the platform provides an easy-to-use Sourcery CodeBench IDE environment which enables better control of the simulation with direct visibility and control of hardware objects (such as registers and values stored in them), tight HW/SW debugging, and file system interactions.

[Sourcery CodeBench HW/SW Debug GUI]

In the tightly coupled HW/SW debugging, hardware simulation can be controlled by setting breakpoint on the access of a hardware object, resetting devices and/or cores, setting simulation mode etc. And there are viewing and analysis facilities for various entities on the display such as hierarchical path to the breakpoint, SystemC simulation time, CPU core tracing, state of DMI (Direct Memory Interface), mode of simulation etc. The Vista Virtual Prototyping supports TLM modelling at LT (Loosely Timed) and AT (Approximately Timed) levels of hardware timing modes. Accordingly, there are two modes of simulation; Functional Mode which corresponds to LT, is fast, and is concentrated at integrating, debugging and validating the software; and Performance Mode which corresponds to AT, is slow, and is concentrated at analyzing and optimizing performance and power consumption. It allows users to select and switch between these timing modes during run time.

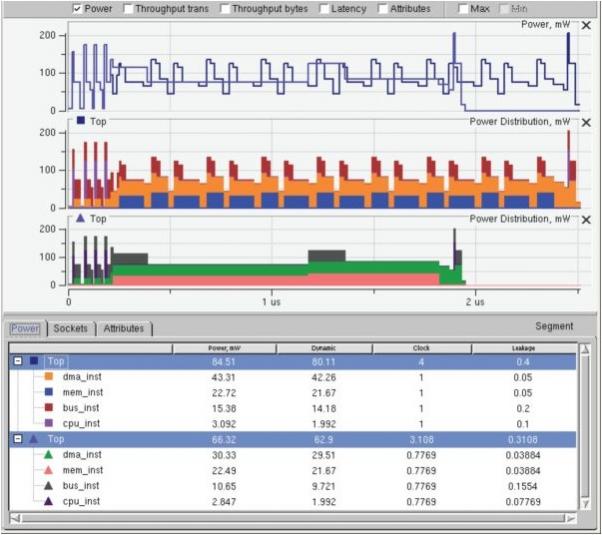

The platform provides excellent viewing and analysis capabilities with reports in graphical, textual or tabular form with varying degrees of granularity and display control on each view as desired by the user. Analysis types like Throughput, Latency, Power (static and dynamic), Power Distribution, Bus Throughput, Contention on bus model (Address phase and Data phase), and Arbitration time (Address and Data) are easily and automatically performed by Vista Virtual Prototyping Analyzer.

[Power distribution comparison of two architectures]

Multiple simulation sessions can be compared to determine the effects of system configuration changes, protocol selection, and software changes on the design behaviour and its performance and power attributes.

An Embedded Sourcery Analyzer conducts software analysis such as CPU State and Statistics, File System Activity, Function Calls and Statistics, Lock Wait and Hold Times, Process and Thread State, Page Fault Rate, Memory Usage and Cache Hit/Miss Ratio.

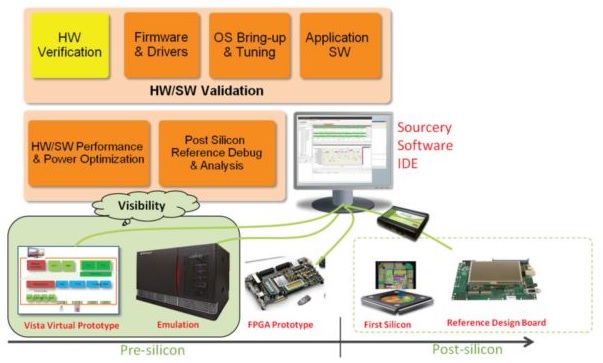

[Native Unified Software IDE across Hardware Evolution]

Vista Virtual Prototyping is integrated into an embedded software design flow that combines validating and optimizing the software on an abstracted simulation model, through emulation, FPGA prototyping during the pre-silicon stage to final product at the post-silicon stage. Users can easily change the underlying hardware model between Vista Virtual Prototypes to hardware prototypes to boards staying within the same native Sourcery IDE.

Click here to download the whitepaper and know more.

Share this post via:

Comments

0 Replies to “Develop A Complete System Prototype Using Vista VP”

You must register or log in to view/post comments.