SystemC version 1.0 came out in 2000 as a C++ class library for system-level modeling and simulation, and on SemiWiki.com there are some 497 references to the language. I wanted to provide an update in this blog so that engineering teams can become more efficient in using SystemC on their SoC projects, saving time and improving product… Read More

Tag: tlm

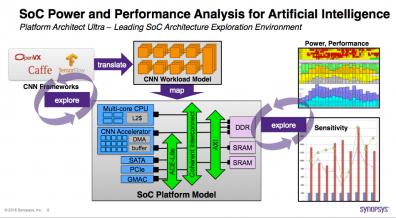

Architecting an ML Design

Discussion on machine learning (ML) and hardware design has been picking up significantly in two fascinating areas: how ML can advance hardware design methods and how hardware design methods can advance building ML systems. Here I’ll talk about the latter, particularly about architecting ML-enabled SoCs. This approach is … Read More

Getting out of DIY Mode for Virtual Prototypes

Virtual prototyping has, inexplicably, been largely a DIY thing so far. Tools and models have come from different sources with different approaches, and it has been up to the software development team to do the integration step and cobble together a toolchain and methodology that fits with their development effort.

That integration… Read More

HLS – Major Improvement through Generations

I am a believer of continuous improvement in anything we do; it’s pleasant to see rapid innovation in technology these days, especially in semiconductor space – technology, design, tools, methodologies… Imagine a 100K gates up to 1M gates design running at a few hundred MHz frequency and at technology node in the range of .18 to … Read More

Designing Hardware with C++ and its Advantages

Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

Transaction-based Emulation

Verification has been going through a lot of changes in the last couple of years. Three technologies that used to be largely contained in their own silos have come together: simulation, emulation and virtual-platforms.

Until recently, the workhorse verification tool was simulation. Emulation had its place but limits on capacity… Read More

Accelerating SoC Verification Through HLS

Once upon a time there was a struggle for verification completion of semiconductor designs at gate level. Today, beyond imagination, there is a struggle to verify a design with billions of gates at the RTL level which may never complete. The designs are large SoCs with complex architectures and several constraints of area, performance,… Read More

Now even I can spot bad UVM

Most programmers can read a code snippet and spot errors, given enough hours in the day, sufficient caffeine, and the right lens prescription. As lines of code run rampant, with more unfamiliar third-party code in the mix, interprocedural and data flow issues become more important – and harder to spot.

Verification IP particularly… Read More

How Do You Verify a NoC?

Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

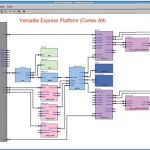

Develop A Complete System Prototype Using Vista VP

Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More