Amidst frequently changing requirements, time pressure and demand for high accuracy, it is imperative that EDA and design companies look at time consuming processes in the overall design flow and find alternatives without losing accuracy. High Frequency Analysis of IC designs is one such process which is traditionally based on models developed using TCAD tools, often leading to approximation in the actual designs. The method is not suitable for architectural exploration which is a prime need today. Moreover considerations of actual interactions among devices and interconnects are necessary.

Mentor Graphics has developed a novel and practical approach to address these issues realistically in live designs on-the-fly. It can extract full chip with automatic detection of HF devices and their accurate characterization taking into account their interaction with neighbouring devices and interconnects. Naturally the approach is quite suitable for design exploration as well; the HFA engine is seamlessly integrated into the various design flows of Calibre platform making it very scalable, user-friendly and production worthy giving performance & capacity boost of 10X compared to traditional TCAD based approach.

It’s interesting to have a look at Mentor’s white paper located at – http://www.mentor.com/resources/techpubs/upload/mentorpaper_74888.pdf. It describes the new modelling and characterization approach in detail. An inductor has been taken as an example for its automatic recognition and characterization. It uses port characterization method which is given in terms of matrix of S-parameters. Effective inductance (L) and quality factor (Q) can be calculated from S-parameters.

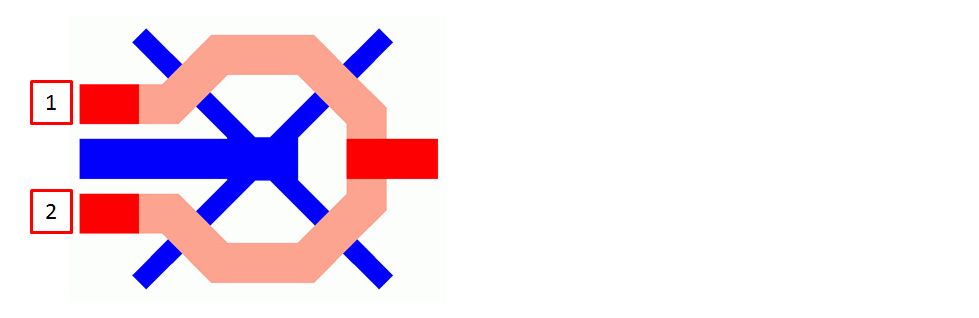

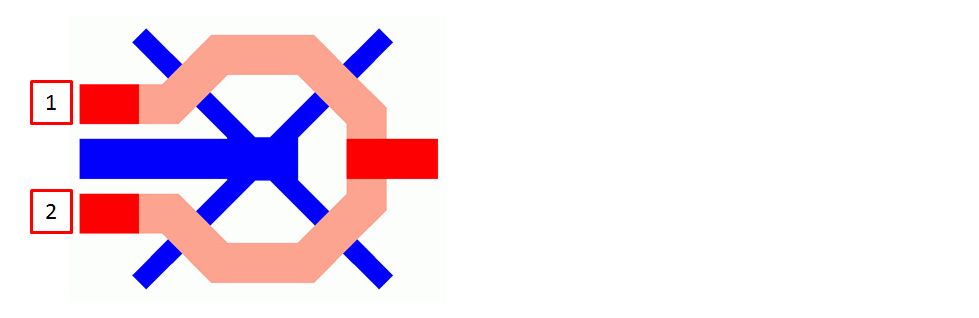

[Example – Inductor layout with assigned ports and a shield (in blue) placed below the inductor to reduce substrate loss]

With the help of SVRF (Standard Verification Rule Format) rule file which has specific information about process layers, port assignments, frequency range etc. Calibreautomatically detects precise inductor geometry from the layout data. Electromagnetic (EM) modelling is used and Calibre EM engine evaluates the integral form of Maxwell equations in the frequency domain, using numerical calculations based on boundary-element method. Special techniques have been employed to control memory consumption and computation time in solving the linear system resulting from the boundary-element method.

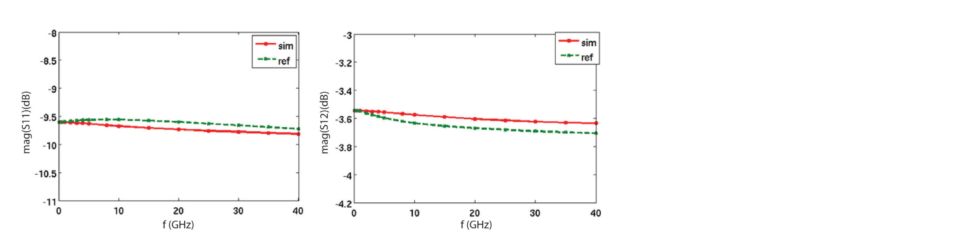

The S-parameter results from Mentor’s new modelling approach are within 2% of those from TCAD.

[Mentor (red) and Reference (green) results for port S-parameters]

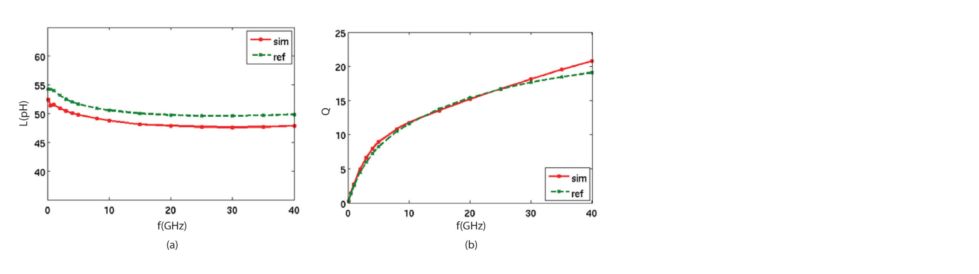

The L and Q values derived from Mentor S-parameters are within 5% and 10% of TCAD based L and Q values respectively.

[L and Q values results from Mentor (red) and Reference (green)]

Mentor’s HFA solution is excellent for practical purposes of design and exploration in quick turn-around-time with high accuracy. Calibre provides integrated platform with excellent usability, scaling and on-the-fly solution. The scalability can be increased further by using multiple CPUs in a multi-threaded, multi-core, or clustered configuration.

Share this post via:

Comments

0 Replies to “New ways for High Frequency Analysis of IC Layouts”

You must register or log in to view/post comments.