I speak VHDL and SystemC, others speak Verilog and SystemVerilog … what do you speak?

Before getting into the core of the topic let me give you some round figures, engineers love numbers. Julian Lonsdale “European Sales Manager at Aldec” informed me at the Xfest Munich last month that Aldec carried out a survey to evaluate the usage of VHDL and Verilog among engineers in the States and Europe and the summary of the results is as follow:

Europe +70% VHDL

USA +50% VHDL

SystemVerilog is booming everywhere

SystemC is saturating or exclusively in research

You can get more details from Saif’s post here:

http://www.eeherald.com/section/news/nws201205137.html

However, Jonathan Bromley “Consultant at verilab” commented when I met him at the SNUG Munich last week that the numbers of the USA might include academic usage which might be deceiving “since academia uses VHDL extensively compared to industry”.

When I was looking for a new job, I have been asked these questions several times;

Would you be willing to learn Verilog instead of VHDL?

In some other cases “Sorry, we are looking for Verilog engineers only?”

As an engineer with more than 9 years experience in the field of digital VLSI, I would reply;

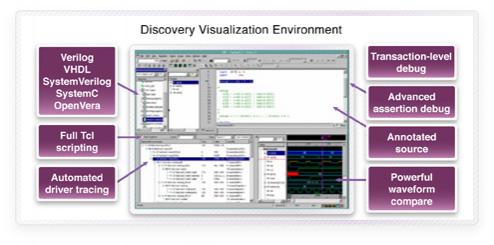

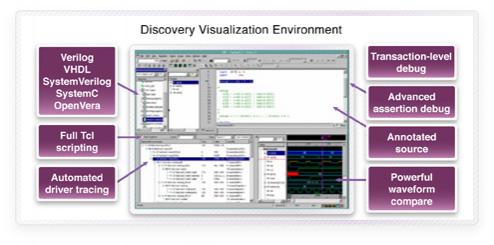

Sure, I can do so but with my experience in VHDL I can interpret each line of code, to how it would be synthesized to hardware. The main difference between VHDL and Verilog is the language syntax. Both are mature and robust. Moreover, all the EDA tools nowadays do support co-simulation/unified environmentas shown in the below figures, i.e., within the same simulation environment we can simulate VHDL, Verilog and SystemC or SystemVerilog as well.

Verilog is the industry standard?

Partially true, at the back-end stage, i.e., place-and-route and exporting the GDSII file most of the EDA tools imports Verilog netlist instead of VHDL netlist. However, this is just a netlist which we can simulate it with the same VHDL testbench, just as an example.

Engineers, should care more about the knowhow and expanding their learning and knowledge horizons with the state-of-the-art methodologies and techniques. Should they develop and acquire new skills in troubleshooting and management. Or they should learn more languages which are literally doing the same thing, in other words a redundancy.

Nowadays, designs/projects are getting more complex, therefore, there is an overlapping between the different engineering tasks. In other words, the front-end engineer should perform a comprehensive functional verification with light formal verification. On the same time, the front-engineer should hand-off to the back-end engineer, consequently he should perform place-and-route and floor-planning as well.

Most of engineers are trying to elaborate or expand their expertise in order to handle complex designs. Therefore, it would be easier to expand effectively with less or efficient time and productivity. As an example, if you are programming in Verilog it would make sense to go for SystemVerilog. In the following table I tried to summarize the main needs for the Hardware Description Languages (HDL), Hardware Verification Languages (HVL) and the Analog and Mixed-Signals languages as follow

[TABLE] align=”center” class=”cms_table_grid” style=”width: 400px”

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” style=”text-align: center” | HDL

| class=”cms_table_grid_td” style=”text-align: center” | HVL

| class=”cms_table_grid_td” style=”text-align: center” | AMS

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | VHDL

| class=”cms_table_grid_td” | OSVVM

| class=”cms_table_grid_td” | VHDL-AMS

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | Verilog

| class=”cms_table_grid_td” | SystemVerilog

| class=”cms_table_grid_td” | Verilog-AMS

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | SystemC

| class=”cms_table_grid_td” | SystemC-SCV

| class=”cms_table_grid_td” | SystemC-AMS

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | .

| class=”cms_table_grid_td” | PSL

| class=”cms_table_grid_td” | .

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | .

| class=”cms_table_grid_td” | e

| class=”cms_table_grid_td” | .

|- class=”cms_table_grid_tr”

| class=”cms_table_grid_td” | .

| class=”cms_table_grid_td” | .

| class=”cms_table_grid_td” | .

|-

There exists more languages, however, those are the most commonly used. The preceding table confirms that most of the HDLs have their own extensions for HVL and AMS as well.

I should point out that PSL has been integrated within VHDL 2008 standard as stated on the following:

http://www.doulos.com/knowhow/vhdl_designers_guide/vhdl_2008/vhdl_200x_major/

http://www.eetimes.com/electronics-news/4154621/VHDL-200x-improves-design-and-verification-productivity

During a coffee break chit-chat with a co-worker from Mexico (speaks Spanish), I asked him “Have you been to Brazil before and do you speak Portuguese as well?” He replied “I can understand Portuguese by more than 80%”. I commented “How come?!”. He explained “Because they are coming from the same root.” Can we say then that VHDL and Verilog has the same root “HDL”!

What about Junior or undergraduate or fresh graduates?

The decision by them is much more difficult nowadays. They have a broad range of languages to select.

A fresher graduate student posted a question “what are the difficulties that face the fresher in the field of VLSI?”. Most of the comments/replies concerned the HDL language that he should learn or use.

From more than 10 years when I was an undergraduate the varieties to choose from was much more limited than nowadays. The HDL selection had a tendency to cope with computer programming and micro-processor architecture courses by that time. In other words, the people who studied Pascal have tendency to VHDL. On the other hand, people who studied C/C++ had more tendency to Verilog. It is very difficult for the undergraduate and even for a graduate to choose certain language to master it nowadays. Check this link to have an overview regarding the standardized languages

http://www.eda.org/

I wish if any employer or decision maker or a team leader who might search for a new candidate to answer those questions and give us a some hand-on the selection preferences.

What exactly you can do using … which you can not do it using …? “fill the spaces with any language within the same category”

Which is more important, the syntax of the design or the documentation “line-by-line comment, help …” of the design itself ?

We are looking forward for your constructive feedback and valuable comments.

Share this post via:

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?