I stopped by the AMIQ EDA booth at DAC to get an update from Tom Anderson about their Integrated Development Environment (IDE), aimed at helping design and verification engineers save time. In my early IC design days we used either vi or emacs and were happy with having a somewhat smart text editor. With an IDE you get a whole new way … Read More

Tag: psl

Next Generation Formal Technology to Boost Verification

With growing complexities and sizes of SoCs, verification has become a key challenge for design closure. There isn’t a single methodology that can provide complete verification closure for an SoC. Moreover creation of verification environment including hardware, software, testbench and testcases requires significant … Read More

A Comprehensive Automated Assertion Based Verification

Using an assertion is a sure shot method to detect an error at its source, which may be buried deep within a design. It does not depend on a test bench or checker, and can fire automatically as soon as a violation occurs. However, writing assertions manually is very difficult and time consuming. To do so require deep design and coding… Read More

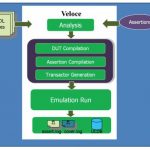

Improving Verification by Combining Emulation with ABV

Chip deadlines and the time to achieve sufficient verification coverage run continuously in a tight loop like a dog chasing its tail. Naturally it is exciting when innovative technologies can be combined so that verification can gain an advantage. Software based design simulators have been the mainstay of verification methodologies.… Read More

How many languages an Engineer should speak?

I speak VHDL and SystemC, others speak Verilog and SystemVerilog … what do you speak?

Before getting into the core of the topic let me give you some round figures, engineers love numbers. Julian Lonsdale “European Sales Manager at Aldec” informed me at the Xfest Munich last month that Aldec carried out a survey to evaluate the usage… Read More