A few weeks ago, I had the chance to work with AMIQ EDA as they introduced a new product: DVT MCP Server. I was quite intrigued by the role it will play in AI-assisted chip design and verification, so I wanted to learn more. I spoke with Gabriel Busuioc, the AI Assistant team leader at AMIQ EDA, to understand more about the product and how… Read More

Tag: vhdl

DVCON U.S. 2026

DVCon is the premier conference on the application of languages, tools, and methodologies for the design and verification of electronic systems and integrated circuits. The focus of the conference is the usage of specialized design and verification languages such as SystemVerilog, Verilog, VHDL, PSS, SystemC and e, as well… Read More

AMIQ EDA Integrated Development Environment #61DAC

I stopped by the AMIQ EDA booth at DAC to get an update from Tom Anderson about their Integrated Development Environment (IDE), aimed at helping design and verification engineers save time. In my early IC design days we used either vi or emacs and were happy with having a somewhat smart text editor. With an IDE you get a whole new way … Read More

Verific at the 2024 Design Automation Conference

Verific Design Automation will host two well-funded AI EDA startups and latest users of Verific’s front-end platform in its Design Automation Conference (DAC) booth, affirming its position as the leading provider of front-end platforms powering an emerging market.

Primis.ai and Silimate, both founded by former chip designers,… Read More

New Tool that Synthesizes Python to RTL for AI Neural Network Code

AI and ML techniques are popular topics, yet there are considerable challenges to those that want to design and build an AI accelerator for inferencing, as you need a team that understands how to model a neural network in a language like Python, turn that model into RTL, then verify that your RTL matches Python. Researchers from CERN,… Read More

The Inconvenient Truth of Clock Domain Crossings

Almost everything that we do in chip design and verification was invented to raise the abstraction above schematics and polygons. Register-transfer-level (RTL) design, functional simulation, logic synthesis, floorplanning, and more fall into this category. Even the notion of binary circuits is an abstraction. Underneath… Read More

Defacto’s SoC Compiler 10.0 is Making the SoC Building Process So Easy

We have been working with Defacto since 2016 and it has been quite a journey. Putting an entire system on a chip is a driving force in the semiconductor industry. With the complexity of designing a modern SoC constantly increasing, new tools and methodologies are required and it all starts with RTL.

Defacto Technologies is an innovative… Read More

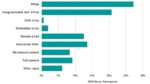

The State of FPGA Functional Verification

Earlier I blogged about IC and ASIC functional verification, so today it’s time to round that out with the state of FPGA functional verification. The Wilson Research Group has been compiling an FPGA report every two years since 2018, so this marks the third time they’ve focused on this design segment. At $5.8 billion… Read More

The State of IC and ASIC Functional Verification

Way back in 2002 there was a study from Collett International Research on functional verification, and since 2010 the Wilson Research Group has continued that same kind of study with a new report every two years. What attracts me to this report is that it doesn’t just look at the installed base of one EDA vendor, instead it looks… Read More

A Hardware IDE for VS Code Fans

A few times a year, I check in with AMIQ EDA co-founder Cristian Amitroaie to see what’s new with their company and the integrated development environment (IDE) market for hardware design and verification. Usually he suggests a topic for us to discuss, but this time I specifically wanted to learn more about the version of their Design… Read More