Last Friday I learned something new about IoT by attending a SEMI event in Wilsonville, OR just a few short miles away from where I live in Tualatin. SEMI puts on two events here in Oregon each year, and their latest event on IoT Sensors was quite timely and popular judging by how many attendees showed up. First up was Jeff Miller from … Read More

Is That PDK Safe to Use Yet?

In our semiconductor ecosystem we have foundries on one side supplying all of that amazing silicon technology, and IC designers on the other side that take their system ideas then go implement them in a SoC using a specific foundry. The required interface between foundry and chip designers has been the Process Design Kit (PDK), … Read More

Semiconductor C-level Executives Explore the Seventh Sense!

The GSA US Executive Forum is in its 5[SUP]th[/SUP] year. It is a time for top level semiconductor executives to meet and try to make sense of a very complex and fast moving industry that has tremendous influence on modern day life. You can see a list of attendees with bios and pictures HERE. There is a lot to talk about (The Future of Drones… Read More

It’s a heterogeneous world and cache rules it now

Cache evolved when the world was all about homogeneous processing and slow and expensive shared memory. Now, compute is just part of the problem – devices need to handle display, connectivity, storage, and other tasks, all at the same time. Different, heterogeneous cores handle different workflows in the modern SoC, and the burden… Read More

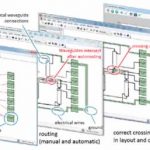

Making photonic design more straightforward

The arrival of optical computing has been predicted every year for the last fifteen years. As with any other technology backed by prolific research, lofty goals get dialed back as problems are identified. What emerges first is a set of use cases where the technology fits with practical, realizable implementations.

When it comes… Read More

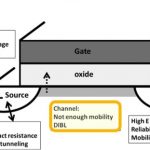

Why is Low Frequency Noise Measurement for ICs Such a Big Deal?

Even digital designers need to be aware of how noise impacts their circuits because most clocked designs today use a Phase Locked Loop (PLL) block which contains a circuit called a Voltage Controlled Oscillator (VCO) that is quite sensitive in operation to the effects of noise and process variation. As process node scaling continues… Read More

The Status and Future of FDSOI

I recently took a look at the current status and future direction of FinFET based logic processes in my Leading Edge Logic Landscape blog. I thought it would be interesting to take a similar look at FDSOI and to compare and contrast the two processes. My Leading Edge Logic Landscape blog is available here.… Read More

Next Book Signing: Linley Processor Conference 2016!

It is a busy month for book signings but it is a pleasure to do it for the greater good of the semiconductor industry. It really is an honor to meet the people who keep our electronic devices on the leading edge of technology, absolutely.

The Linley Processor Conference is on September 27[SUP]th[/SUP]and 28[SUP]th[/SUP] at the Hyatt… Read More

CEO Interview: Xerxes Wania of Sidense

This is the first in a series of CEO interviews and I thought semiconductor IP would be a great place to start. Xerxes Wania is the President and CEO of Sidense, a leading developer of Non-Volatile Memory (NVM) One-Time Programmable (OTP) IP cores. Sidense has been a part of SemiWiki since 2013 so we know them quite well. I hope the rest… Read More

We Don’t Need Graphic Design. We Do Need Graphic Views

Many years ago, there were attempts to (re-) introduce a graphical entry approach to building RTL design. The Renoir product was one example. The idea has some initial appeal. You describe the behavior in a small block using (textual) RTL but the larger structure of instances and higher-level connectivity can be described as a … Read More