TSMC attends DAC every year and they do something very savvy, it’s a theatre where they invite all of their EDA and IP partners to present something of interest, followed by a drawing for a prize. At the end of the day they even have a nice prize, like a MacBook Air, which I didn’t win. On Wednesday I watched Dave Reed of Synopsys… Read More

In Their Own Words: TSMC and Open Innovation Platform

TSMC, the largest and most influential pure-play foundry, has many fascinating stories to tell. In this section, TSMC covers some of their basic history, and explains how creating an ecosystem of partners has been key to their success, and to the growth of the semiconductor industry.

The history of TSMC and its Open Innovation … Read More

400G Ethernet test chip tapes-out at 7nm from eSilicon

Since the beginning of May eSilicon has announced the tape-out of three TSMC 7nm test chips. The first of these, a 7nm 400G Ethernet Gearbox/Retimer design, caught my eye and I followed up with Hugh Durdan, their vice president of strategy and products, to learn more about it. Rather than just respin their 56G SerDes, they decided… Read More

An evolution in FPGAs

Why does it seem like current FPGA devices work very much like the original telephone systems with exchanges where workers connected calls using cords and plugs? Achronix thinks it is now time to jettison Switch Blocks and adopt a new approach. Their motivation is to improve the suitability of FPGAs to machine learning applications,… Read More

Learning on the Edge Investment Thesis

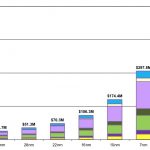

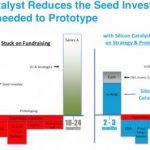

It is said that it will cost as much as $600M to develop a 5nm chip. At that price, only a few companies can afford to play, and with that amount of cash in, innovation is severely limited.

At the same time, there is a stampede in the artificial intelligence (AI) market where around 60 startups have appeared, many of which have already … Read More

Re Energizing Silicon Innovation

Hardware is roaring back into prominence in technology innovation, from advanced cars to robots, smart homes and smart cities, 5G communication and the burgeoning electronification of industry, medicine and utilities. While software continues to play a role, all of these capabilities depend fundamentally on advances in … Read More

TSMC and Samsung 5nm Comparison

Samsung and TSMC have both made recent disclosures about their 5nm process and I though it would be a good time to look at what we know about them and compare the two processes.

A lot of what has been announced about 5nm is in comparison to 7nm so we will first review 7nm.

7nm

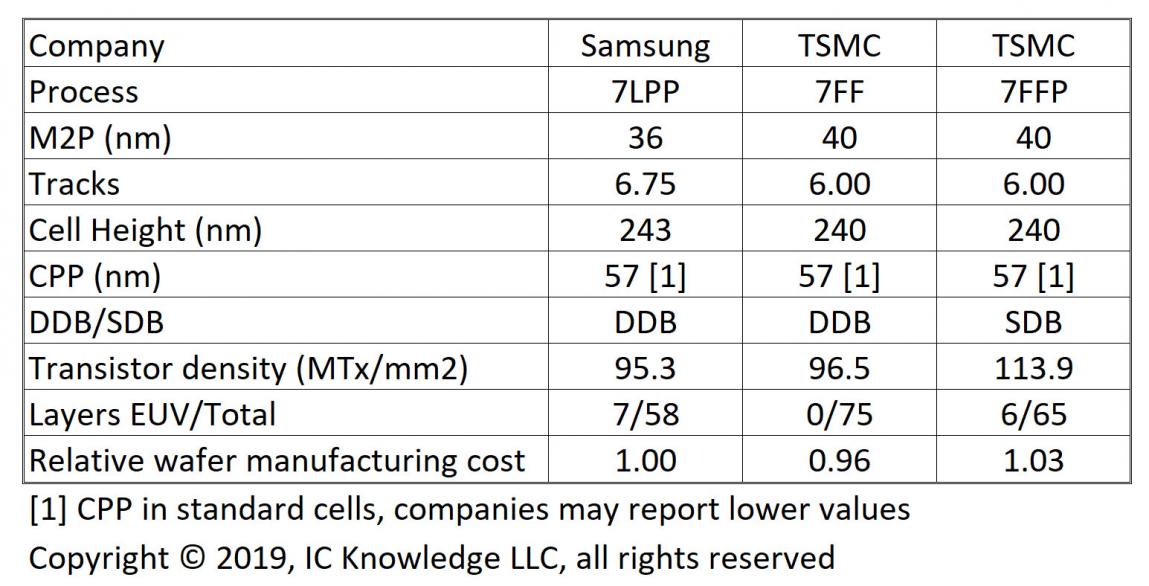

Figure 1 compares Samsung’s 7LPP process to TSMC’s 7FF and 7FFP… Read More

TSMC Technology Symposium Review Part II

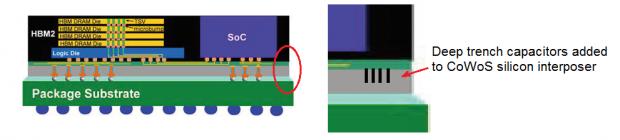

TSMC recently held their annual Technology Symposium in Santa Clara. Part 1 of this article focused on the semiconductor process highlights. This part reviews the advanced packaging technologies presented at the symposium.

TSMC has clearly made a transition from a “pure” wafer-level foundry to a supplier of complex integrated… Read More

2019 TSMC Technology Symposium Review Part I

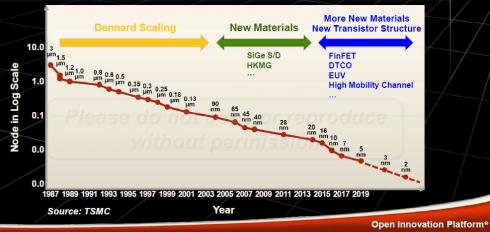

Each year, TSMC conducts two major customer events worldwide – the TSMC Technology Symposium in the Spring and the TSMC Open Innovation Platform Ecosystem Forum in the Fall. The Technology Symposium event was recently held in Santa Clara, CA, providing an extensive update on the status of advanced semiconductor and packaging… Read More

A Quick TSMC 2019 Tech Symposium Overview

This year TSMC did a FinFET victory lap with the success of 16nm, 12nm, 10nm, and 7nm. It really is well deserved. Even though TSMC credits the ecosystem and customers, I credit TSMC and their relationship with Apple since it has pushed us all much harder than ever before. TSMC CEO C.C. Wei summed it up nicely in his keynote: Innovation,… Read More