After mentioning what I heard at IEDM 2018, that Intel was officially closing the merchant foundry business as an aside in a SemiWiki forum discussion, I got a lot of email responses so let me clarify. Honestly I did not think it was a big surprise. Intel Custom Foundry was an ill conceived idea (my opinion) from the very start and was… Read More

Samsung IEDM 2018 Keynote and the Foundry Business

IEDM is a premier semiconductor conference so it was certainly appropriate for Samsung to do the keynote since they are the largest and one of the most innovative semiconductor companies in the world, absolutely.

Samsung is also one of the more interesting semiconductor companies since they do it all: chip design, semiconductor… Read More

Intel Diversity Semiconductors

Growing up in a military family, mostly in California, I would consider my cultural diversity life experience to be more than most. I remember in the 1960s some older folks were chattering about a colored family moving into our neighborhood and they had a son my age. Imagine my excitement as a child in having a multicolored friend!… Read More

GlobalFoundries Pivots in China

China has always been an intriguing semiconductor puzzle that very few companies have solved and now it is much more puzzling with the current political meandering. The GlobalFoundries vision of having foundries all over the world was very appealing to me back in 2009 and even more so today. Remember, China consumes more than half… Read More

The Latest from Samsung Semiconductor

Earlier this Spring, Samsung Foundry held a technology forum, describing their process roadmap and supporting ecosystem developments (link). Recently, the larger Samsung Semiconductor organization conducted a Tech Day at their campus in San Jose, presenting (and demo-ing) a broader set of products. The focus of the day was… Read More

Intel Q3 2018 Jibber Jabber

This is what happens when you have a CFO acting as a semiconductor CEO, and Robert Holmes is a career CFO with zero semiconductor experience or education. Granted, no way did he write the opening statement, but it was full of jibber jabber anyway. The real disappointing jibber jabber was from our own Murthy Renduchintala on the status… Read More

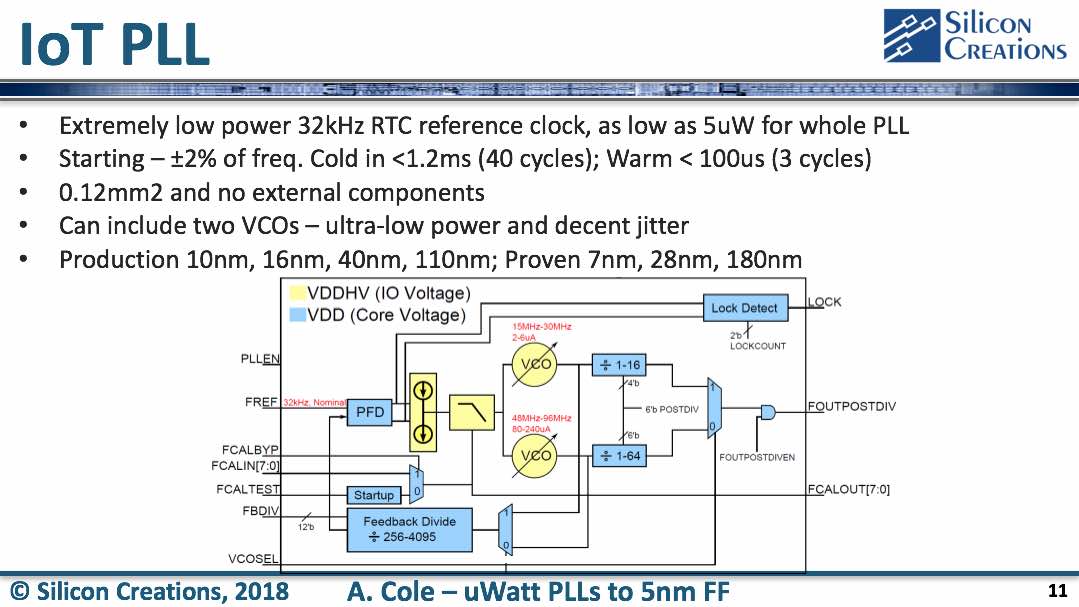

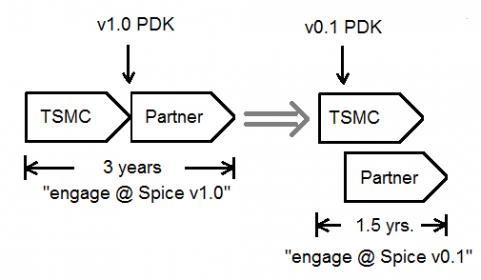

Essential Analog IP for 7nm and 5nm at TSMC OIP

When TSMC’s annual Open Innovation Platform Exposition takes place, you know it will be time to hear about designs starting on the most advanced nodes. This year we were hearing about 7nm and 5nm. These newer nodes present even more challenges than previous nodes due to many factors. Regardless of what kind of design you are undertaking… Read More

Webinar: ASIC and FPGA Functional Verification Study

ASIC or FPGA? Each design style has earned designers’ votes depending on the level of urgency, application complexity and funding of their assigned projects. While it is feasible to transition from ASIC to FPGA design or vice versa, such a move is usually done across project refresh instead of midcourse.

TSMC Q3 2018 Earnings Call Discussion!

The TSMC OIP Forum was very upbeat this year and now we know why. It wasn’t long ago that some media outlets and a competitor said 7nm would not be a popular node because it is too expensive blah blah blah. People inside the fabless semiconductor ecosystem however know otherwise. As I have said before, 7nm will be another strong node … Read More

Top 10 Highlights from the TSMC Open Innovation Platform Ecosystem Forum

Each year, TSMC hosts two major events for customers – the Technology Symposium in the spring, and the Open Innovation Platform Ecosystem Forum in the fall. The Technology Symposium provides updates from TSMC on:

… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!