We all knew this quarter would be big but maybe not this big. Not all good news though so keep on reading. The news coverage is all over the map, mostly because they have no idea what a pure-play foundry really is. They also underestimate the power of mobile computing which should be a “Revenue by Application” market segment itself. … Read More

How has 20nm Changed the Semiconductor Ecosystem?

What does mango beer have to do with semiconductor design and manufacturing? At a table of beer drinkers from around the world I would have never thought fruity beer would pass a taste test, not even close. As it turns out, the mango beer is very good! Same goes for 20nm planar devices. “Will not work”, “Will not yield”, “Will not scale”,… Read More

Intel Opens a New Front with ASML

Behind great humor often lies irony. In the midst of a struggle by the European Union to extract $1.3B from Intel in an ages old Anti-Trust case, the latter makes a strategic move to embolden the Dutch firm ASML to accelerate the development of 450mm and EUV and thus save a continental jewel. What now say EU? When disfunction and bankruptcy… Read More

Intel Goes Vertical to Guarantee PC Growth

A Bloomberg article from early July caught my eye as it portends further changes in the competitive mobile market landscape. Intel is now in the business of paying Taiwanese panel suppliers to ensure the supply of touch-screen panels for PC ultrabooks. In essence it says that to win in the PC market, Intel has to mimic Apple and go … Read More

Intel’s finfets too complex and difficult?

Thanks to SemiWiki readers for the feedback and comments on the previous “Introduction to FinFET Technology” posts – very much appreciated! The next installment on FinFET modeling will be uploaded soon.

In the interim, Dan forwarded the following link to me “ Intel’s FinFETs too complicated and difficult, says … Read More

Dragon Boats and TSMC 20nm Update!

My luck continues as I missed last week’s typhoon. Fortunately it did not disrupt the annual Dragon Boat Festival. More than just a Chinese tradition, dragon boat racing is an international sports event with teams from around the world coming to Taiwan every year. It is very exciting with the colorful dragon boats and the wild beating… Read More

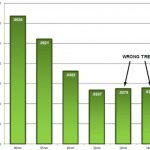

The Scariest Graph I’ve Seen Recently

Everyone knows Moore’s Law: the number of transistors on a chip doubles every couple of years. We can take the process roadmap for Intel, TSMC or GF and pretty much see what the densities we will get will be when 20/22nm, 14nm and 10nm arrive. Yes the numbers are on track.

But I have always pointed out that this is not what drives… Read More

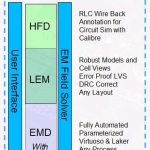

TSMC Threater Presentation: Lorentz Solution!

Lorentz Solution presented at TSMC’s DAC 2012 Open Innovation Platform Theater. The presenter was Lorentz Sales Director, Tom Simon. He presented what Lorentz calls its Electromagnetic Design and Analysis Platform. One of the main points of the talk was the cooperative work that Lorentz does with TSMC.

TSMC Threater Presentation: Solido Design Automation!

For a small company, Solido has some very large customers and partners, TSMC being on of them. Why? Because of the high yield and memory performance demand on leading edge technologies, that’s why.

Much has been made of and will continue to be said on the march of Moore’s Law. While economics of scale and performance vs. power… Read More

Samsung, Synopsys, GLOBALFOUNDRIES and ARM at DAC

Tuesday morning at DAC I attended the Synopsys-hosted breakfast to hear from foundries and ARM about the challenges of designing and delivering silicon at the 32nm/28nm and 20nm nodes.

… Read More

ASML High-NA EUV is Not Ready for High-Volume Production