The “1.xnm” node on most roadmaps to indicate a 16-18 nm metal line pitch [1]. The center-to-center spacing may be expected to be as low as 22-26 nm (sqrt(2) times line pitch). The EXE series of EUV (13.5 nm wavelength) lithography systems from ASML feature a 0.55 “High” NA (numerical aperture), targeted… Read More

LAM Not Yet at Bottom Memory Worsening Down 50%

-Lam reported in line results on reduced expectations

-Guidance disappoints as memory decline continues

-Memory capex down 50% but still sees “further declines”

-Lam ties future to EUV maybe not good idea after ASML report

Lam comes in above grossly already reduced expectations

and misses on guidance

We always … Read More

ASML Wavering- Supports our Concern of Second Leg Down for Semis- False Bottom

-ASML weakness is evidence of deeper chip down cycle

-When ASML sneezes other chip equip makers catch a cold

-Will backlog last long enough? Will EUV demand hold up?

-“Unthinkable” event, litho cancelations, could shock industry

ASML has in line quarter but alarm bells ring on wavering outlook

ASML reported Euro6.7B… Read More

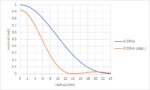

Can Attenuated Phase-Shift Masks Work For EUV?

Normalized image log-slope (NILS) is probably the single most essential metric for describing lithographic image quality. It is defined as the slope of the log of intensity, multiplied by the linewidth [1], NILS = d(log I)/dx * w = w/I dI/dx. Essentially, it gives the % change in width for a given % change in dose. This is particularly… Read More

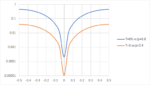

Lithography Resolution Limits: The Point Spread Function

The point spread function is the basic metric defining the resolution of an optical system [1]. A focused spot will have a diameter defined by the Airy disk [2], which is itself a part of the diffraction pattern, based on a Bessel function of the 1st kind and 1st order J1(x), with x being a normalized coordinate defined by pi*radius/(0.5… Read More

Sino Semicap Sanction Screws Snugged- SVB- Aftermath more important than event

-Reports of further tightening of China SemiCap Restrictions

-Likely closing loopholes & pushing back technology line

-Dutch have joined, Japan will too- So far no Chinese reaction

-SVB is toast but repercussions may be far worse

Reports of tightening semiconductor sanctions on Friday

It was reported byBloomberg of Friday… Read More

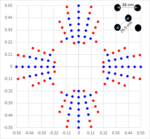

Resolution vs. Die Size Tradeoff Due to EUV Pupil Rotation

The many idiosyncrasies of EUV lithography affect the resolution that can actually be realized. One which still does not get as much attention as it should is the cross-slit pupil rotation [1-3]. This is a fundamental consequence of using rotational symmetry in ring-field optical systems to control aberrations in reflective… Read More

KLAC- Weak Guide-2023 will “drift down”-Not just memory weak, China & logic too

-Business will “drift down” over the course of 2023

-Not just memory is weak- China issue, foundry/logic slowing

-March guide worse than expected (Like Lam)

-Backlog likely saw push outs & cancelations but still long

Good quarter but weak guide

Much as we saw with Lam, KLA reported a beat on the December quarter… Read More

U.S., Japan & Dutch versus China Chips & Memory looks to be in a long downturn

-US, Japan & Dutch agree to embargo some China chip equip

-Goes beyond just leading edge & will increase negative impact

-China might catch up in decades or invade Taiwan tomorrow

-Why the memory downturn could be longer than expected

Ganging up on China

It appears that the US has put together a coalition of the US, Japan and… Read More

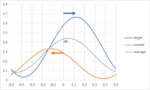

Multiple Monopole Exposures: The Correct Way to Tame Aberrations in EUV Lithography?

For a leading-edge lithography technology, EUV (extreme ultraviolet) lithography is still plagued by some fundamental issues. While stochastically occurring defects probably have been the most often discussed, other issues, such as image shifts and fading [1-5], are an intrinsic part of using reflective EUV optics. However,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center