You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 16126

[name] => Lithography

[slug] => lithography

[term_group] => 0

[term_taxonomy_id] => 16126

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 187

[filter] => raw

[cat_ID] => 16126

[category_count] => 187

[category_description] =>

[cat_name] => Lithography

[category_nicename] => lithography

[category_parent] => 0

[is_post] =>

)

– Strong demand across logic/memory & leading/trailing edge

– Customers want units fast-no time to test

– The main question is can ASML ramp to meet demand?

Revenue & Earnings low due to systems being rushed to customers

ASML reported Euro 4B in sales and Euro 1B in net income which while within guidance… Read More

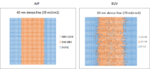

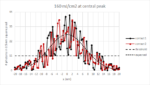

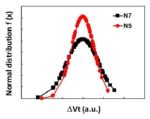

Due to the higher energy of EUV (13.3-13.7 nm wavelength) compared to ArF (193 nm wavelength) light, images produced by EUV are more susceptible to photon shot noise.

Figure 1. (Left) 40 nm dense (half-pitch) line image projected onto wafer at 35 mJ/cm2; (Right) 20 nm dense (half-pitch) line image projected onto wafer at 70 mJ/cm2.… Read More

The stochastic behavior of images formed in EUV lithography has already been highlighted by a number of authors [1-3]. How serious it appears depends on the pixel size with which the photons are bunched. Generally, though, for features of around 20 nm or less, even 1 nm can have at least a +/- 15% gradient across it, which is still a

…

Read More

– KLA put up an excellent quarter and Guide

– Rising above the increasing tide of orders

– Confirms $75B capex in 2021 with upside

– Foundry & Logic continue to be the sweet spot for KLA

Business is very very good and getting better

-Revenues came in at $1.8B with EPS of $3.85, all above the range

-Guidance… Read More

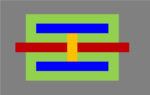

In this article, we will explore the use of self-aligned litho-etch-litho-etch (SALELE) double patterning for BEOL metal layers in the 7nm node (40 nm minimum metal pitch [1]) with DUV, and 5nm node (28 nm minimum metal pitch [2]) with EUV. First, we mention the evidence that this technique is being used; Xilinx [3] disclosed the… Read More

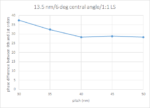

At the SPIE Advanced Lithography Conference held in February, ASML presented the latest information on their Deep Ultraviolet (DUV) and Extreme Ultraviolet (EUV) exposure systems. I recently got to interview Mike Lercel of ASML to discuss the presentations.

DUV

Despite all the attention EUV is getting, most layers are still… Read More

I recently posted an insightful article [1] published in 2013 on the cost of 3D NAND Flash by Dr. Andrew Walker, which has since received over 10,000 views on LinkedIn. The highlight was the plot of cost vs. the number of layers showing a minimum cost for some layer number, dependent on the etch sidewall angle. In this article, the same… Read More

– ASML has good quarter driven by DUV & Logic (@72%)

– SMIC & other major customer slow EUV plans

– Logic (read that as TSMC) remains key demand led driver

– We are happy memory remains muted given cyclical potential

A very solid quarter with a continued road to growth

The quarter came in at Euro4,254B… Read More

For advanced lithography used to shrink semiconductor device features according to Moore’s Law, resolution limits are an obvious consideration. It is often perceived that the resolution limit is simply derived from a well-defined equation, but nothing can be further from the truth.

Optical Lithography: the fine print

…

Read More

The vast majority of the attention given to the introduction of each new advanced process node focuses on lithographic updates. The common metrics quoted are the transistors per mm**2 or the (high-density) SRAM bit cell area. Alternatively, detailed decomposition analysis may be applied using transmission electron microscopy… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era