Toshiba (now known as Kioxia) was the first company to propose a 3D stacked version of NAND Flash memory called BICS [1]. BICS (BIt Cost Scalable) Flash used explicit process cost reduction based on depositing and etching multiple layers at once, avoiding multiple lithography steps. This strategy replaced the usual approach of shrinking the unit cell size, and at the same time, replaced the floating gate charge storage element with a nitride layer containing charge-trapping defects.

As a result of this new approach, the actual cell footprint is much larger than in previous generations of NAND Flash. The process integration is also very different, which makes the wafer cost difficult to judge. However, a model for the cost per bit was provided by Toshiba [2], relative to that of a planar NAND (32nm when disclosed in 2009). Additionally, hints of the size of the 3D NAND cell have recently become available [3,4]. With these pieces of information, a model of wafer cost is now possible to draw out.

Toshiba’s Cost per Bit model for 3D (2009)

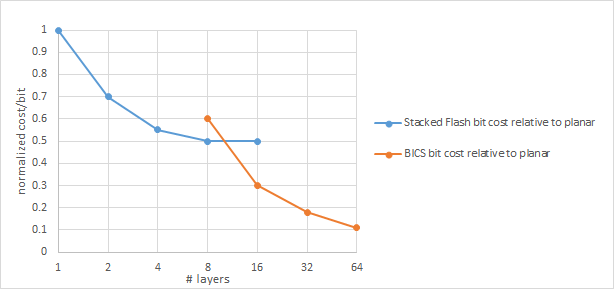

Toshiba disclosed the cost per bit advantage of its BICS 3D NAND scheme in 2009 (Figure 1).

Figure 1. Toshiba’s cost per bit, relative to planar. Since this was published in 2009, 32nm planar Flash is expected to be the reference. Source: Reference [2].

It is quite clear that Toshiba is highlighting the bit cost advantage of its BICS scheme, compared to the standard stacked 3D Flash case. This advantage would also for 3D Crosspoint schemes for resistance-based memories.

While cost per bit is relevant to selling the product, the technology development is more sensitive to cost per wafer. How does that trend?

Bits per wafer: BICS vs. planar

The size of the BICS unit cell is shown in Figure 2. The ~100 nm diameter of the channel was disclosed as early as 2010 [4], but the actual electron micrographs showing unit cells were not available until the end of 2019 [3].

Figure 2. Plan view of BICS unit cell, based on [3] and [4]. The four sections of the channels at each corner add up to a complete one.

From this picture we get a unit cell area within a single layer of 130 nm x 150 nm, or 19500 nm^2. For N layers, the effective cell size is divided by the factor N. On the other hand, for reference, the 32 nm planar NAND cell stays at a fixed area of 64 nm x 64 nm, or 4096 nm^2. With the bit cell area known, we can calculate the bits per 300mm wafer. Then, by multiplying the cost/bit by bits/wafer, we can get the cost/wafer.

Cost per wafer: 3D vs planar

The cost per wafer thus obtained is shown in Figure 3. Also shown is the expected wafer cost for continued 2D planar scaling, assuming same costs for 22nm and 32nm, and 20% extra cost (e.g., extra patterning for 20% of layers for SADP to SAQP transition) for 16nm and 11nm. Since these costs are all relative to the 32 nm planar case, a further simplifying assumption is made that the area efficiency is the same for all cases.

Figure 3. Wafer cost for BICS vs stacked 3D vs planar scaling. 32 nm planar NAND is the reference for BICS and stacked 3D wafer cost.

The simply stacked 3D cost rises higher than BICS, due to the repetition of many complex lithography-related process steps. On the other hand, planar scaling is relatively flat, but rises slowly for 1X generations. Interestingly, the BICS wafer cost is also flat up to 16 layers, before starting to rise slowly. The close proximity of continued planar scaling and BICS wafer costs could also explain the longevity of the former, as shown in Figure 4. In that figure, as in Figure 3, the layer number axis is kept for the scaled planar case, to reflect the “effective layer number” based on the scaled cell size.

Figure 4. Bit cost of planar scaling compared to stacked 3D and BICS.

It would be expected that 16nm is still competitive with 16-layer BICS. If the assumed 20% extra cost for 16nm were an overestimate, or depreciated, then 16nm could remain competitive even longer. On the other hand, scaled planar NAND has the fundamental disadvantage of always having peripheral CMOS circuitry outside the array, consuming wafer area (therefore adding cost). In contrast, the 3D approach in principle has the option of putting such circuitry under the array. Stacking of two layers of 11nm NAND Flash (if it existed) can possibly match the bit cost of 64-layer BICS, but the wafer cost would be 40% higher, resulting in just being a little more expensive than the 64-layer BICS case. Despite the relatively lower bit cost, the wafer cost of BICS-style 3D NAND is still increasing with layer count, for 32 layers and more. This is further complicated by the addition of string stacking [5], which is the equivalent of double/multiple patterning in the vertical direction.

The Bigger Picture: total system costs

It should be remembered that even with the lower cost/GB offered by 3D NAND, the total cost of the system using the 3D NAND chip has to include that of the fairly expensive controller chip used to guarantee the reliability (endurance, retention, etc.) of the stored bits. This is especially so when more than one bit is stored per cell. The controller is fabbed at advanced foundry nodes, and is a well-known source of heat (see e.g., [6]). The heat must be dissipated to prevent degradation of the NAND performance, so special heat sinking is needed as well. These all add to the cost of operating a 3D NAND chip.

Alternative memory candidates could offer better reliability, and therefore not require the expensive controller or special heat sink. Furthermore, new in-memory computing paradigms may be supported (see e.g., [7]). It may be expected that although the initial bit costs are high, scaling for such alternative memories would follow the same path as 3D NAND, due to the demonstrated bit cost reduction.

References

[1] A. Nitayama et al., “Bit Cost Scalable (BiCS) technology for future ultra high density storage memories,” 2007 Symposium on VLSI Technology.

[2] https://savolainen.wordpress.com/2011/12/

[3] https://www.systemplus.fr/wp-content/uploads/2019/12/SP19483-3D-NAND-Memory-Comparison-2019_Sample.pdf

[4] T. Ichikawa et al., “Topography simulation of BiCS memory hole etching modeled by elementary experiments of SiO2 and Si etching,” SISPAD 2010.

[5] https://semiengineering.com/how-to-make-3d-nand/

[6] https://www.tomshardware.com/reviews/samsung-980-pro-m-2-nvme-ssd-review

[7] https://arxiv.org/pdf/1906.06603.pdf

Share this post via:

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!