A lot of the attention in intelligent systems is on object detection in still or video images but there’s another very active area, in smart audio. Amazon and Google smart speakers may be the best-known applications but there are more obvious (and perhaps less novelty-driven) applications in enhancing the hearing devices we already… Read More

Semiconductor Intellectual Property

Early IP Block Error Detection is Critical!

The rising complexity of modern SoC designs, as enabled by progressing manufacturing technology, leads to an increasing validation challenge as the only way to manage complexity increase is by re-using more pre-designed IP blocks. These IP-blocks are provided by various suppliers such as a foundry partner, internal design… Read More

Two Fun Things To Do at SEMICON West on July 9, 2019

I will be at SEMICON / EE Design West on Tuesday, July 9, 2019, and so should you!

Quantum computing will be a hot topic at SEMICON West and on Tuesday, July 9, the IBM Quantum Computer will be on display at the Smart Design Pavilion in the South Hall (Moscone Center) from 10:00am to 5:00pm. It looks like no other computer I have ever… Read More

2019 GSA Silicon Summit and SiFive

Naveed Sherwani, President and CEO of SiFive, did the keynote for this year’s Silicon Summit. This is one of the premier events for the C level executives in Silicon Valley, absolutely. Naveed is one of the top visionaries for the semiconductor industry and he certainly did not disappoint this time or any other time in my experience.… Read More

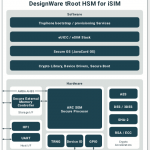

Integrated SIMs Will Unlock IoT Growth

I’m a believer that connectivity for the IoT at scale (the trillions of devices that the industry predicts) has to be cellular. This is partly based on reach, particularly outside urban areas, but is mostly based on the financial implications of that scale. Yes, you can build infrastructure for say local Wi-Fi support with backhaul… Read More

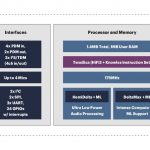

Eta Compute Showcases Continuously Tuned DVFS

If you practice in advanced levels of power management, you know about dynamic voltage and frequency scaling (DVFS). This is where you allow some part of a circuit, say a CPU, to run at different voltages and frequencies depending on acceptable performance versus thermal tradeoffs and battery life on a mobile device. Need to run… Read More

ARM Spins New IP for Client Applications

Arm is a machine. They crank out new products in a wide range of categories, Project Trillium for AI, Neoverse for infrastructure, their Automotive Enhanced line and the Pelion IoT platform. And in each they have a regular beat of new product introductions following roadmaps they have already laid out. Not that you’d expect any … Read More

Considering SiFive: What Should I Get to Implement a RISC-V Core?

I have an old weathered leather-clad black notebook with a National Semiconductor logo on its face that I have used since 2001. It has sentimental value to me. First, it reminds me of where I was on 9/11, having breakfast with a group of attendees to National Semiconductor’s executive event in Laguna Niguel, CA. We were going to play… Read More

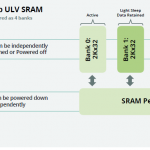

Custom SRAM IP @56thDAC

The electronics industry strives to continuously introduce new product innovation and differentiation. The ASIC market arose from the motivation to offer unique (cost-reduced) integration that was not realizable with commodity MSI/LSI parts. The SoC market evolved to provide even greater differentiation, integrating… Read More

#56thDAC SerDes, Analog and RISC-V sessions

The good news is that the next five DAC events will take place in Moscone Center in San Francisco! If going to Las Vegas from the Bay area is an easy trip, coming from Europe to Las Vegas makes it a 24+hours journey… One obvious consequence was the poor attendance to the exhibition floor. But let’s be positive and notice that the number… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era