80% of specification optimization and almost 100% of the performance/power trade-offs can be achieved during architecture exploration of product design. RISC-V offers a huge opportunity with lots of pipeline and instruction set enhancement opportunities. Can it really attain the utopian success that people are looking… Read More

Semiconductor Intellectual Property

Podcast EP30: Interview with Tony Pialis, Alphawave IP

Dan is joined by Tony Pialis. Tony co-founded Alphawave in 2017 and has since served as its President and Chief Executive Officer. The journey of Alphawave is discussed, including differentiation, strategy and the IPO as well as a look to the future.

Tony co-founded Alphawave in 2017 and has since served as its President and Chief… Read More

Architecture Exploration with Miribalis Design

Architectural exploration is a vast area of engineering design. It starts with the planning phase where the designer will have the list of requirements from the customer and the rough architecture most likely on a paper. Next is to assemble the model and conduct variety of trade-offs for optimization and functional studies to … Read More

A Hardware Security Standard Advances

Security is a slippery topic. We all agree that “something should be done”, but most of us are waiting for someone else to lead the way. There’s no shortage of proprietary solutions, though given the distributed nature of the problem it’s difficult to see how those separately or collectively can rise to the occasion. What we really… Read More

Cadence Tensilica FloatingPoint DSPs

Being engrossed in the digital information world, it is easy to forget that the real world is comprised of mostly analog signals and data. Digital Signal Processors (DSP) take digitized forms of these worldly signals and manipulate them mathematically. Although floating-point is a more relevant and accurate way of representing… Read More

StarFive Surpasses Development Goal with the Prodigy Rapid Prototyping System from S2C

Faced with the challenge of developing a high-performance hardware platform with critical software components, what choices do companies have in rapidly moving their development forward with modest budgets and resources?

That was the challenge faced by StarFive Technology, a leading IP and semiconductor SoC platform solution… Read More

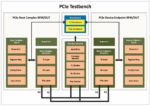

PCIe Gen 6 Verification IP Speeds Up Chip Development

PCIe is a prevalent and popular interface standard that is used in just about every digital electronic system. It is used widely in SOCs and in devices that connect to them. Since it was first released in 2003, it has evolved to keep up with rapidly accelerating needs for high speed data transfers. Each version has doubled in throughput,… Read More

The Zen of Auto Safety – a Path to Enlightenment

Safety is a complex topic, but we’re busy. We take the course, get the certificate. Check, along with a million other things we need to do. But maybe it’s not quite that simple. I talked recently with Kurt Shuler (VP of marketing) and Stefano Lorenzini (functional safety manager) at Arteris IP and concluded that finding enlightenment… Read More

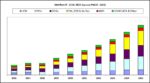

IPnest Forecast Interface IP Category Growth to $2.5B in 2025

Why should the interface IP category see such a high growth rate until 2025? IP vendors revenues totaled $1068 million in 2020, compared with $872 in 2019. That is 22.4% YoY growth rate and confirm that last year YoY value of 18% was the sign for a long-term growth, as IPnest shows in “Interface IP Survey 2016-2020 & Forecast 2021-2025”,… Read More

Safety + Security for Automotive SoCs with ASIL B Compliant tRoot HSMs

Automotive segment is a market that has historically been supported by a few select suppliers within the semiconductor ecosystem. Over the last decade, this market has transitioned from just being about reliability, performance, fuel efficiency, etc., to placing equal importance to user experience. This user experience … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center