You may have seen this Press Release (see below) announcing that Dolphin Integration (Dolphin) has been acquired by Soitec (60%) and MBDA (40%) – you can see more information about these two companies at the bottom of this blog. Founded in 1985, Dolphin had some recurrent cash flow issues during the last couple of years, that they… Read More

Semiconductor Intellectual Property

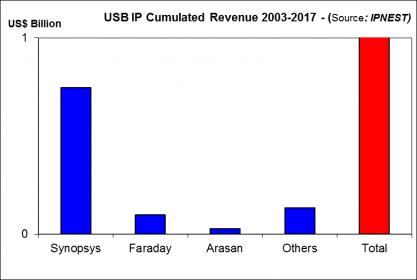

USB 3.x IP Revenue Have Grown by 31% in 2017 (IPnest)

Despite the strong consolidation in the semiconductor industry, the Design IP market is going well, very well with YoY growth of 12%+ in 2017, according with the “Design IP Report” from IPnest. If we look at the Interface IP category (20% growth in 2017) and analyze the IP revenues by protocols, we can see that USB IP is amazingly healthy,… Read More

The Robots are Coming!

Moshe Sheier, VP Marketing at CEVA, recently got back from MWC Shanghai and commented that robots are clearly trending. He saw hordes of robots from dozens of companies, begging for someone to brand and offer them in any one of many possible applications: in an airport to guide you to a connecting flight, for elder care, in hospitals… Read More

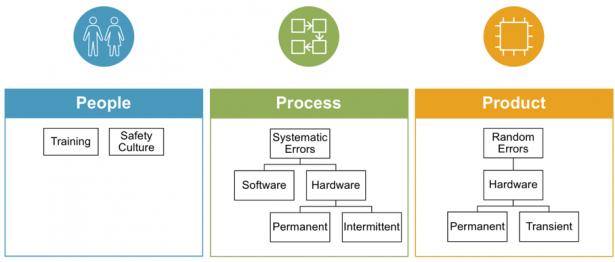

ISO 26262: People, Process and Product

Kurt Shuler, VP Marketing at Arteris IP, is pretty passionate that people working in the automotive supply chain should understand not just a minimalist reading of ISO 26262 as it applies to them but rather the broader intent, particularly as it is likely to affect others higher in the supply chain. As an active ISO 26262 working … Read More

Improving Yield and Reliability with In-Chip Monitoring, there’s an IP for that

There’s an old maxim that you can only improve what you measure, so quality experts have been talking about this concept for decades and our semiconductor industry has been the recipient of such practices to such an extent that we can now buy consumer products that include chips with over 5 billion transistors in them. You’ve… Read More

Webinar: Ensuring System-level Security based on a Hardware Root of Trust

A root of trust, particularly a hardware root of trust, has become a central principle in well-architected design for security. The idea is that higher layers in the stack, from drivers and OS up to applications and the network, must trust lower layers. What does it help it to build great security into a layer if it can be undermined… Read More

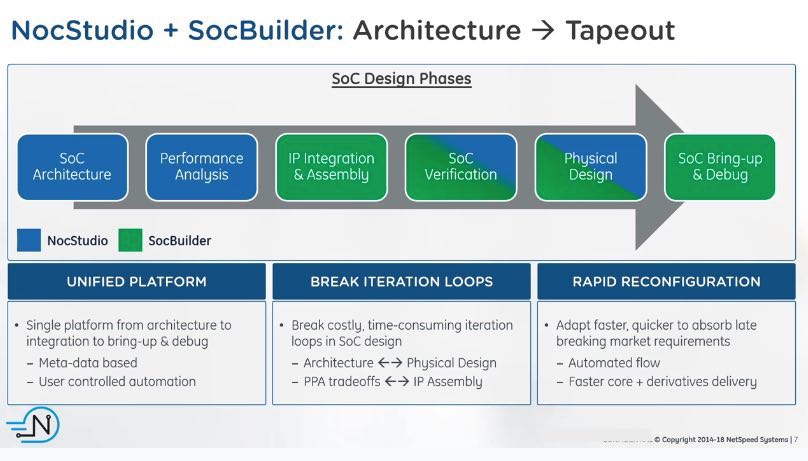

Webinar: NetSpeed is about to change the way SOCs are designed

A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More

Measuring Up 7nm IP

The Linley Group is an industry-leading source for independent technology analysis of semiconductors for networking, communications, mobile, and data-center applications. Their Microprocessor Report is widely read as a source of un-biased, no-nonsense analysis of technologies and trends. So, when they dig into something… Read More

Enabling Complex System Design Environment

Deterministic, yet versatile. Robust and integrated, yet user-friendly and easily customizable. Those are some desirable characteristics of an EDA solution as the boundaries of our design optimization, verification and analysis keep shifting. A left shift driven by a time-to-market schedule compression, while the process… Read More

eSilicon and SiFive partner for Next-Generation SerDes IP

While writing “Mobile Unleashed: The Origin and Evolution of ARM Processors In Our Devices” it was very clear to me that ARM was an IP phenomenon that I did not believe would ever be repeated. Clearly I was wrong as we now have RISC-V with an incredible adoption rate, a full fledged ecosystem, and top tier implementers… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era