Charlie Janac is president and CEO of Arteris IP where he is responsible for growing and establishing a strong global presence for the company that is pioneering the concept of NoC technology. Charlie’s career spans over 20 years and multiple industries including electronic design automation, semiconductor capital equipment,… Read More

Interconnect Basics: Wires to Crossbar to NoC

To many of us, if we ever think about interconnect on an SoC, we may think delay, power consumption, congestion, that sort of thing. All important points from an implementation point of view, but what about the functional and system implications? In the early days, interconnect was very democratic, all wires more or less equal, … Read More

Where’s the Value in Next-Gen Cars?

Value chains can be very robust and seemingly unbreakable – until they’re not. One we’ve taken for granted for many years is the chain for electronics systems in cars. The auto OEM, e.g. Toyota, gets electronics module from a Tier-1 supplier such as Denso. They, in turn, build their modules using chips from a semiconductor chip maker… Read More

Design in the Time of COVID

There’s a lot of debate about how and when we are going to emerge from the worldwide economic downturn triggered by the pandemic. Everyone agrees we will emerge. This isn’t humanity’s first pandemic, nor will it be our last. But do we come out quickly or slowly? And what does the economy look like on the other side, particularly for … Read More

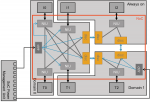

AI, Safety and Low Power, Compounding Complexity

The nexus of complexity in SoC design these days has to be in automotive ADAS devices. Arteris IP highlighted this in the Linley Processor Conference recently where they talked about an ADAS chip that Toshiba had built. This has multiple vision and AI accelerators, both DSP and DNN-based. It is clearly aiming for ISO 26262 ASIL D … Read More

That Last Level Cache is Pretty Important

Last-level cache seemed to me like one of those, yeah I get it, but sort of obscure technical corners that only uber-geek cache specialists would care about. Then I stumbled on an AnandTech review on the iPhone 11 Pro and Max and started to understand that this contributes to more than just engineering satisfaction.

Caching

A brief… Read More

Trends in AI and Safety for Cars

The potential for AI in cars, whether for driver assistance or full autonomy, has been trumpeted everywhere and continues to grow. Within the car we have vision, radar and ultrasonic sensors to detect obstacles in front, behind and to the side of the car. Outside the car, V2x promises to share real-time information between vehicles… Read More

Autonomous Driving Still Terra Incognita

I already posted on one automotive panel at this year’s Arm TechCon. A second I attended was a more open-ended discussion on where we’re really at in autonomous driving. Most of you probably agree we’ve passed the peak of the hype curve and are now into the long slog of trying to connect hope to reality. There are a lot of challenges, … Read More

Evolving Landscape of Self-Driving Safety Standards

I sat in a couple of panels at Arm TechCon this year, the first on how safety is evolving for platform-based architectures with a mix of safety-aware IP and the second on lessons learned in safety and particularly how the industry and standards are adapting to the larger challenges in self-driving, which obviously extend beyond … Read More

Safety and Platform-Based Design

I was at Arm TechCon as usual this year and one of the first panels I covered was close to the kickoff, hosted by Andrew Hopkins (Dir System Technology at Arm), Kurt Shuler (VP marketing at Arteris IP) and Jens Benndorf (Managing Dir and COO at Dream Chip Technologies). The topic was implementing ISO 26262-compliant AI SoCs with Arm… Read More