First, a quick definition. By “structured assembly,” I mean the collection of tools to support IP packaging with standardized interfaces, SoC integration based on those IPs together with bus fabric and other connectivity hookups, register definition and management in support of hardware/software interface definition, together with collateral support functions such as document generation and traceability. In other words, automation technologies in and around the IEEE 1685 (IP-XACT) standard or other systems with similar objectives.

I have been involved with structured assembly in one way or another for almost 20 years, first in developing our own product at Atrenta and later in writing about Magillem’s better-known IP-XACT line of products. I’m a believer in the concept – you can’t integrate billion-gate SoCs with a text editor. But, the commercial product opportunity has not been as clear. I have seen significant resistance to commercial products for small designs or small teams, understandably, but also for big designs among teams with their own highly tuned and specialized integration methodologies and software. Magillem from Arteris, has marquee logos to their credit (NXP, Samsung, STM, for example), but are commercial IP-XACT technologies stuck at the chasm or have they crossed?

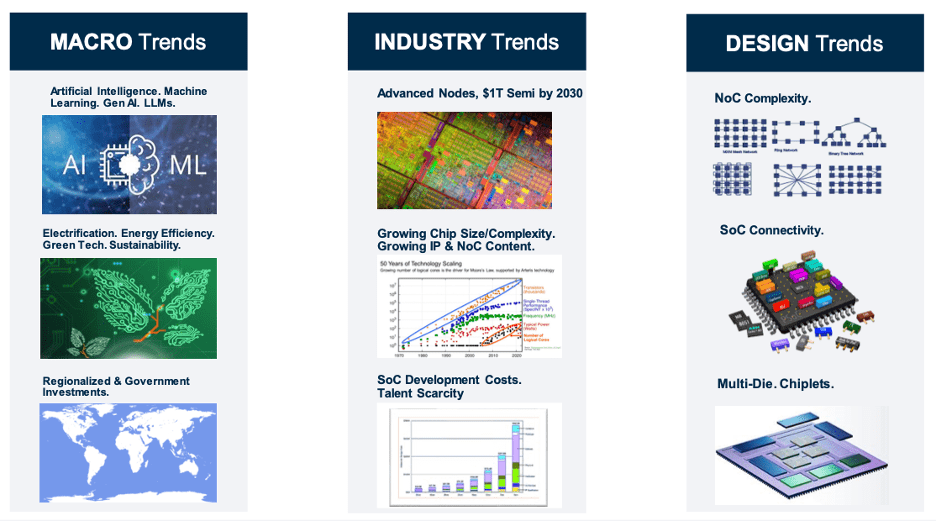

(Graphic Source: Arteris, Inc)

New Marketing Team, New Vision

Michal Siwinski joined Arteris almost 2 years ago as CMO, shortly followed by a team of industry experts. They have been re-engineering big chunks of the Arteris company, product strategy, solution pitch, customer engagement, and brand starting, of course, with the NoC technologies. I must admit I have been impressed. They have a new, fresh approach to positioning Arteris NoC technologies in the fast-evolving world of HPC / AI / multi-die systems / automotive / edge and, no doubt, other domains. So, I was interested to see what they would do with Magillem and my perceived crossing-the-chasm problem.

I was encouraged that Michal understood why I felt the way I did. He had similar experiences with a Cadence attempt at such a product (I’m sure shared by counterparts at Synopsys). He agreed that adoption across the overall industry is not high. But when he looks at the top 10, 50 or 100 semis and system companies building big chips, they are all using structured assembly in some form. In that sense, the technology has already crossed the chasm. That said, CAD and individual design teams are given a lot of freedom in which assembly solution they adopt for their own projects, even when there is a centralized standard. Some organizations standardize on Magillem, some on an in-house standard (though mergers have made this option less common), and many vary from product team to product team. That said, Michal sees those home-grown systems coming under increasing pressure in what seems a perfect storm of disruptions triggered by macro, industry, and design trends.

The Gathering Storm

Disruptions force re-engineer/buy decisions for in-house software. You can rebuild the system to adapt to a change, or you can buy a system that already handles that change. Nothing new here – disruptions pretty much drove the evolution of the entire EDA and IP industry. In-house solutions work best until the cost of keeping up with evolving demands outweighs the benefits. At some point, often different for different design teams, a switch may become less costly than re-architecting the home-based tool.

One such trigger in this instance is the release of the IP-XACT 2022 standard. Michal tells me there are several semantic changes, such as more compatibility with SystemVerilog features, which will force rework to in-house systems. Equally important, there are changes to deal with really large systems, which may be even more challenging for re-engineering projects.

A second problem is that tiled subsystems are becoming more popular: in AI, in many-core compute, and in graphics cores. The disruption here is a scaling problem because the complexity of interconnect that must be hooked up between these tiles rises dramatically. Not impossible to handle in a legacy system, but the effort to create and rework and the opportunity for errors can grow quadratically given the nature of these structures.

A third challenge is the growing diversity of sources for IP, external for the standard stuff but now also for AI cores, DSPs in support of AI pipelines, sensing and sensor fusion, eFPGA and multi-die connectivity. Internal cores from other divisions and design partners add to this complexity, each commonly in different flavors of IP-XACT. This isn’t a technology challenge; it’s an administrative volume challenge, particularly as we move to from dozens to 100s of IP blocks that make up a chip, but even more so when that number goes even higher, perhaps across multiple die . Technology challenges are fun to take on internally; administrative/scaling problems not so much and this is where EDA and IP companies excel.

Another disruption comes from a trend to continuous integration (CI) flows in SoC design, something I heard hints of back at the beginning of the Innovation in Verification series. As designs become more specialized to meet more application-specific needs and schedules tighten, it is natural to plan families of derivatives which must be pushed out in even tighter schedules. Michal is now hearing of design flows with an 80%-ready core as a base, from which different derivatives can evolve even while the base itself may continue to evolve.

Then, of course, there is multi-die design, in which some “IPs” will be pre-designed chiplets with pre-determined interface constraints for communication, power management, version compatibility issues, etc., etc. Meanwhile, boundaries between proposed chiplets can remain fluid until quite late in design but with enhanced need for careful control of implications for implementation.

The End Is Nigh

In short, Michal sees a perfect storm building of new and evolving demands on integration platforms. Perhaps not all will be important immediately to a given product plan, but then you start to worry about how long you can continue to kick the can down the road until a transition becomes unavoidable. Either way, it seems clear there will be building pressure to re-evaluate tradeoffs between in-house solutions with significant re-engineering costs on the horizon, versus a planned and controlled switch to commercial platforms.

You can learn more about Arteris Magillem solutions for SoC connectivity HERE, for register management HERE, for hardware/software interface development HERE, and learn more about some public customers HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.