There was an article on Motley Fool recently detailing Intel’s 14nm FinFETs and comparing them to TSMC. Unfortunately the author has zero semiconductor education or experience even though he writes with authority on all things semiconductor. He also has no shame in using outdated papers from conferences he did not even… Read More

FinFET vs FDSOI – Which is the Right One for Your Design?

As a professional conference goer I can see definite trends when it comes to topics and attendance. Thus far this year I have seen a double digit increase in attendance, which is great. The question is why? Why is the fabless semiconductor ecosystem leaving the safety of their cubicles and computer screens in droves to mingle amongst… Read More

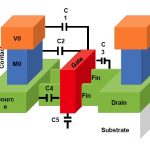

FinFET Design Enablement

We read about FinFET technology in the semiconductor press daily now, thanks to Intel introducing their TriGate transistors starting in 2011 and creating a race with foundries and IDMs to switch from planar CMOS nodes. To get some perspective about the progress of FinFET IP and EDA tools I spoke with two experts from Synopsys, Swami… Read More

2015, the Year of the Sheep…And the 16nm FPGA

If you live in California anyway, with its large Asian population, you can’t have helped noticing that it was the Lunar New Year a couple of weeks ago, the start of the year of the sheep. A couple of days after the New Year, Xilinx announced their new families of what they now call FPGAs, 3D ICs and MPSoCs. But which the rest of us … Read More

Xilinx’s 16nm UltraScale+ FPGA is Revolutionary

Well a very belated Happy New Year dear reader. I must admit, it has been a very long winter and it has caused the Miller’s to rethink this vital question. “What in the world are we doing living in NY”. So we are moving, and hopefully this is my last ‘real’ winter as we headed down south. To perhaps alleviate some of the winter blues from … Read More

Samsung 14nm IS in Production!

There is quite a debate raging on whether Samsung Foundry is truly in production at 14nm. The word amongst the fabless semiconductor ecosystem is yes and this comes from two very large fabless companies that are reportedly using Samsung for 14nm and have even started looking at Samsung 10nm. Of course you can Google for stories by… Read More

TSMC’s OIP: Everything You Need for 16FF+ SoCs

Doing a modern SoC design is all about assembling IP and adding a small amount of unique IC design for differentiation (plus, usually, lots of software). If you re designing in a mature process then there is not a lot of difficulty finding IP for almost anything. But if you are designing in a process that has not yet reached high-volume… Read More

Altera Back to TSMC at 10nm? Xilinx Staying There

Xilinx announced their quarterly results last week. They slightly missed their number due mainly to a decline in wireless sales. Of course Xilinx parts don’t go in the smartphones since the cost and power are too high, but they are very heavily used in basestation, backhaul etc especially in China. Xilinx’s business… Read More

Which Foundry will be First to FinFET?

The final session of the SEMI Industry Strategy Symposium (The CxO Panel) was the most interesting for me because executives from three of the four most influential semiconductor companies were on the panel: Dr. Goeff Yeap of Qualcomm, Dr. Jack Sun from TSMC, and Mr. Mark Bohr of Intel. Who is fourth you ask? That would be Apple of … Read More

ANSYS Updates RedHawk for FinFET Nodes

Most designers are not using FinFETs yet, however the increased transistor density and power advantages they offer are compelling. Smaller feature sizes have been a consistent driver in semiconductor technology. Eventually the market will move more and more to FinFET processes, increasingly leaving behind planar transistors.… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era