I’ve been visiting DAC for decades now, at first as an EDA vendor and since 2004 as a freelance EDA consultant. There’s always a buzz about what’s new, semiconductor industry trends, who is getting acquired and the latest commercial EDA and IP offerings. There’s so much vying for my attention at DAC each… Read More

HOT Party for a Cause at DAC 55

The Design Automation Conference (DAC), now in its 55[SUP]th[/SUP] year, always offers a lively mix of activities. For EDA vendors and their customers, the focus is on the exhibit floor and in booth suites where the latest technology is on display. For R&D engineers and academics, the technical sessions dig deeply into an … Read More

TSMC OIP DAC Theater Schedule 2018

The TSMC OIP DAC Theater schedule is finalized and ready to go. It kicks off Monday at 10:15 am in booth #1629 and ends with a raffle at 5:45 pm each day (Mon-Tue-Wed) TSMC gives out some very nice prizes so check in with the TSMC booth staff when you arrive. There are 66 coveted presentation spots representing the top ecosystem partners… Read More

The Best of IP at DAC 2018 Conference

Design IP is going well, with 12% YoY growth in 2017, even if the market is about $3.5B. But Design IP is serving a $400B semiconductor market. Can you imagine the future of the semi market if the chip makers couldn’t have access to Design IP? The same is true for EDA: it’s a niche market (CAE revenues was about $3B and IC Physical Design… Read More

Imec technology forum 2018 – the future of memory

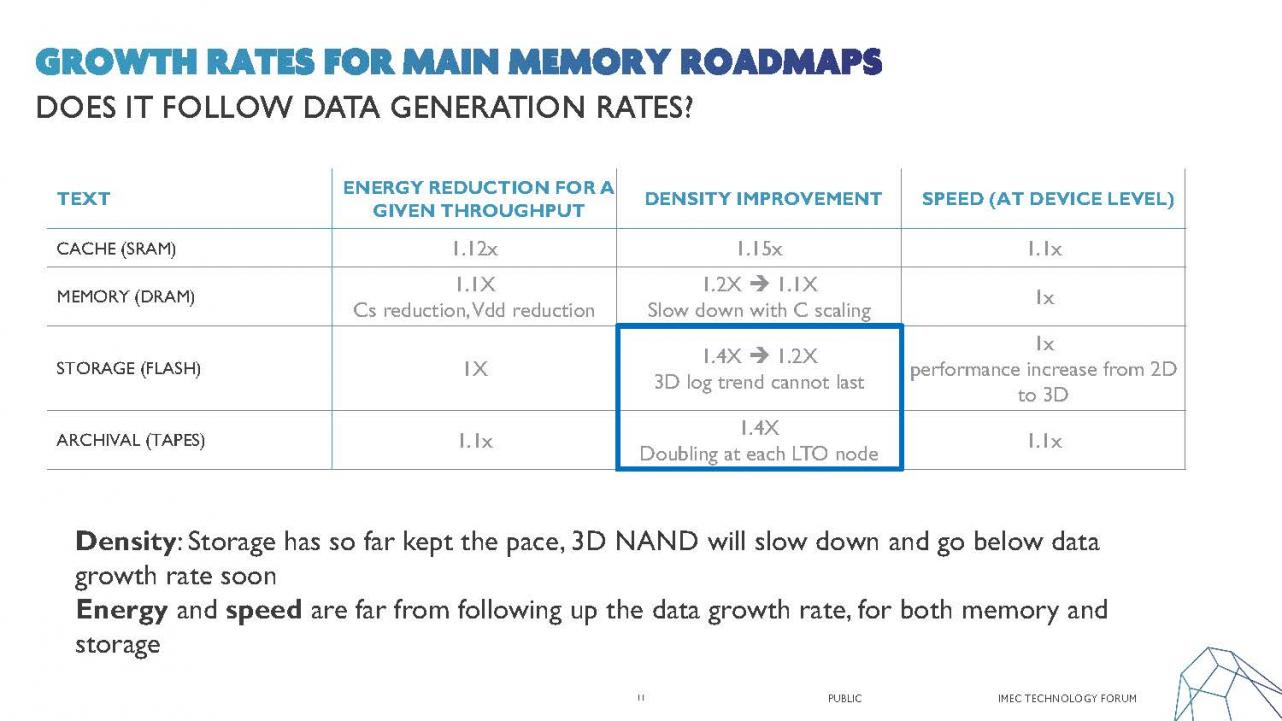

At the Imec technology forum in Belgium Gouri Sankar Kar and Arnaud Furnemont presented memory and storage perspectives and I also got to interview Arnaud. Arnaud leads overall memory development at Imec and personally leads NAND and DNA research.

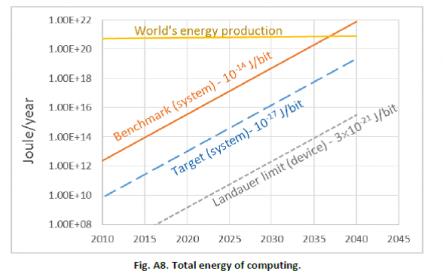

Memory research is focused on power, energy, speed and cost with energy and throughput… Read More

The Dawn of a New RISC

The 8[SUP]th[/SUP] RISC-V Workshop was held in Barcelona May 7-10 with 325 attendees from 150+ companies and was the biggest RISC-V event outside of Silicon Valley, demonstrating the momentum of the RISC-V Foundation and the growth of the ecosystem in Europe.… Read More

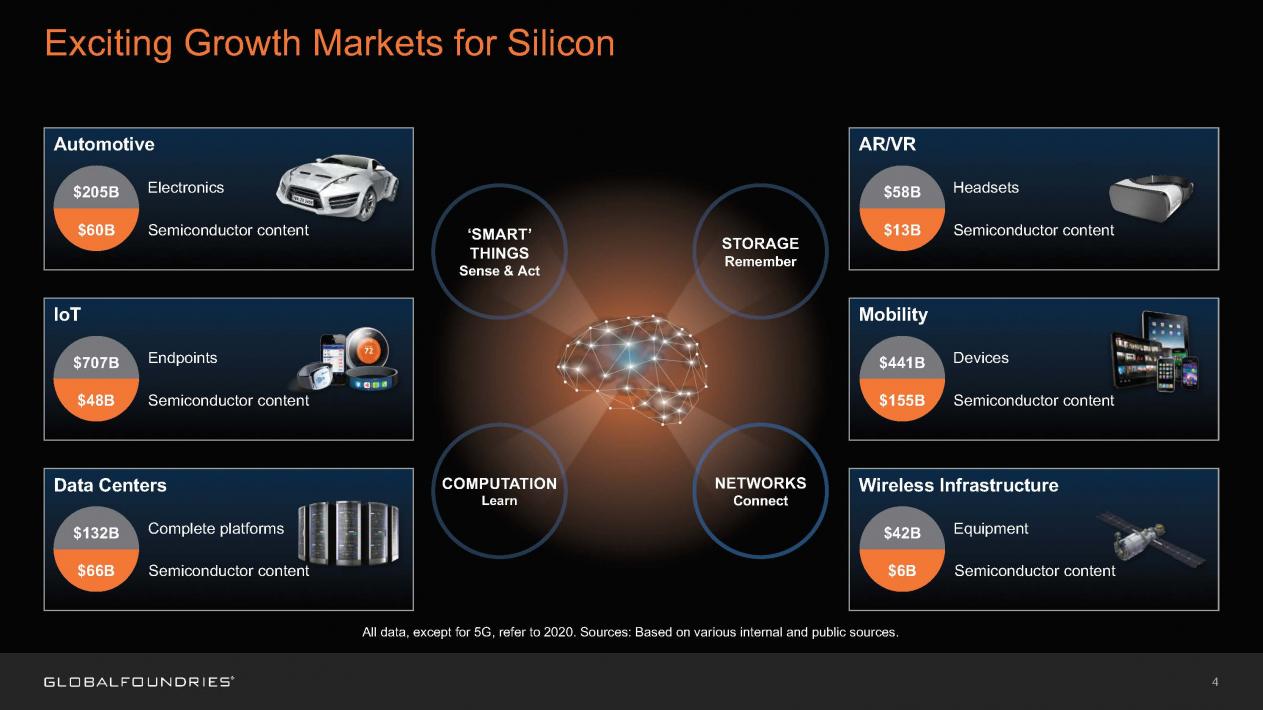

Imec Technology Forum: Gary Patton of GLOBALFOUNDRIES

The imec technology forum was held in Belgium last week. At the forum I had a chance to sit down with Gary Patton the CTO of GLOBALFOUNDRIES (GF) for an interview and he also presented “Enabling Connected Intelligence – Technology innovation: Enablers for an intelligent future” at the forum. In this article … Read More

Webinar: RISC-V IoT Security IP

Disruptive technology and disruptive business models are the lifeblood of the semiconductor industry. My first disruptive experience was with Artisan Components in 1998. The semiconductor industry started cutting IP groups which resulted in a bubble of start-up IP companies including Artisan, Virage Logic, Aspec Technologies,… Read More

UBER car accident: Verifying more of the same versus the long-tail cases

The recent fatal accident involving an UBER autonomous car, was reportedly not caused – as initially assumed – by a failure of the many sensors on the car to recognize the cyclist. It was instead caused by a failure of the software to take the right decision in regard to that “object”. The system apparently… Read More

TSMC Technologies for IoT and Automotive

At TSMC 2018 Silcon Valley Technology Symposium, Dr Kevin Zhang, TSMC VP of Business Development covered technology updates for IoT platform. The three growth drivers in this segment namely TSMC low power, RF enhancement and embedded memory technology (MRAM/RRAM) reinforced both progress and growth in global semiconductor… Read More

TSMC N3 Process Technology Wiki