You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 50

[name] => Events

[slug] => events

[term_group] => 0

[term_taxonomy_id] => 50

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 1533

[filter] => raw

[cat_ID] => 50

[category_count] => 1533

[category_description] =>

[cat_name] => Events

[category_nicename] => events

[category_parent] => 0

[is_post] =>

)

If you are considering an FPGA prototype for an ASIC or SoC as part of your verification strategy, which more and more chip designers today are doing to enhance verification coverage of complex designs, please take advantage of this webinar replay:

How ASIC/SoC Prototyping Solutions Can Help You!

Or to get a quick quote from S2C … Read More

The old adage that “Time is Money” certainly rings true in the semiconductor world where IC designers are being challenged with getting their new designs to market quickly, and correctly in the first spin of silicon. Circuit designers work at the transistor-level, and circuit simulation is one of the most time-consuming… Read More

By its very definition, machine learning (ML) hardware requires flexibility. In turn, each ML application has its own fine grain requirements. Specific hardware implementations that include specialized processing elements are often desirable for machine learning chips. At the top of the priority list is parallel processing.… Read More

I have heard many times before that low power and mixed-signal design is more Art than Science. I believe this is a misconception. Science is a field that builds upon previous experiences and discoveries. Art primarily seeks out creative differences, things we have not seen before that evoke emotion. The most successful designers… Read More

Last year at Semicon I sat down with Soitec and got an update on the company. You can read my write up from last year here. A key point last year was Soitec was continuing to be profitable and grow after several years of financial struggles.

On Thursday, July 11th I got to sit down with Soitec’s CEO, Paul Boudre and get an update on… Read More

When it comes to security we’re all outraged at the manifest incompetence of whoever was most recently hacked, leaking personal account details for tens of millions of clients and everyone firmly believes that “they” ought to do better. Yet as a society there’s little evidence beyond our clickbait Pavlovian responses that we’re… Read More

In SoC design it’s all about managing complexity through modeling, and the models that make up IC designs come in a wide range of file formats like:

- Transistor-level , SPICE

- Interconnect parasitics, SPEF

- Gate and RTL, Verilog, VHDL

Even with standard file formats, designers still have to traverse the hierarchy to find out… Read More

As more than 343 people (and counting) know, we will be releasing the 2019 updated PDF version of our first book “Fabless: The Transformation of the Semiconductor Industry” via handout at a live webinar. The response has been overwhelming and I want to personally thank you. The webinar will be a brief overview of the book with a question… Read More

The need to design low power devices is not new. However, the criticality of lowering the power consumption of chip designs has never been as important as it is now. In 1989, I purchased one of the first consumer cell phones produced by Panasonic. The battery was the size of a brick, but only about a third of the thickness. If the battery… Read More

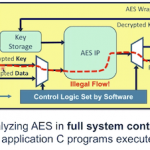

We all know (I hope) that security is important so we’re willing to invest time and money in this area but there are a couple of problems. First there’s no point in making your design secure if it’s not competitive and making it competitive is hard enough, so the great majority of resource and investment is going to go into that objective.… Read More

Is Intel About to Take Flight?