Exciting times for the semiconductor industry! Last week Intel announced a billion dollar fund to build a foundry ecosystem and today Intel announced they are acquiring foundry Tower Semiconductor for $5.6 billion dollars, WOW! Some people doubted Intel’s commitment to the foundry market this time. I think we can now put that… Read More

Upcoming Webinar: Optimized Chip Design with Main Processors and AI Accelerators

Using the right tool for the job can be extremely important. Well, maybe not in the case of the famed chef Martin Yan who is notorious for using just one knife—a razor sharp wide blade cleaver that doubles as a spatula—for preparing anything and everything he cooks. For the rest of us, though, the right tools can make all the difference.… Read More

Accellera at DVCon U.S. 2022 in the Metaverse!

The premier verification conference and exhibition is coming up and of course Accellera plays an important role. This year DVCON will again be virtual, which is unfortunate, but I must say as a long time attendee this year’s program really stands out. In fact, there is a new addition that is worth mentioning, it’s the… Read More

Future of Semiconductor Design: 2022 Predictions and Trends

Predictions and trends create the forces that accelerate innovations and keep the industry moving forward. We are all used to hearing of important issues and challenges, usually in the context of solutions offered by various vendors. The SemiWiki forum plays its role in bringing awareness of all of the above to its audience. For… Read More

Are We Headed for a Semiconductor Crash?

COVID was certainly a black swan event but semiconductors have seen similar events over the past 50 years, some of which I have experienced personally. The Dot-com bubble comes to mind but there were others. The question is will history repeat itself and the answer, according to Malcolm Penn of Future Horizons, is yes.

Malcolm is… Read More

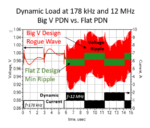

WEBINARS: Board-Level EM Simulation Reduces Late Respin Drama

Advanced board designs are fertile ground for misbehavior in time and frequency domains. Relying on intuition, then waiting until near-final product for power integrity (PI) or EMI testing almost guarantees board respins are coming. Lumped-parameter simulations of on-board power delivery networks (PDNs) struggle with … Read More

WEBINAR: How to add a NIST-Certified Random Number Generator to any IoT device?

In the first half of 2021, the number of attacks on IoT devices more than doubled to 1.5 billion attacks in just six months. These attacks target some typical weaknesses, such as the use of weak passwords, lack of regular patches and updates, insecure interfaces, and insufficient data protection. However, researchers from Bishop… Read More

Samsung Keynote at IEDM

Kinam Kim is a longtime Samsung technologist who has published many excellent articles over the years. He is now the Chairman of Samsung Electronics, and he gave a very interesting keynote address at IEDM.

He began with some general observations:

The world is experiencing a transformation powered by semiconductors that has been… Read More

Upcoming Webinar: 3DIC Design from Concept to Silicon

Multi-die design is not a new concept. It has been around for a long time and has evolved from 2D level integration on to 2.5D and then to full 3D level implementations. Multiple driving forces have led to this progression. Whether the forces are driven by market needs, product needs, manufacturing technology availability or EDA… Read More

How System Companies are Re-shaping the Requirements for EDA

As the oldest and largest EDA conference, the Design Automation Conference (DAC) brings the best minds together to present, discuss, showcase and debate the latest and greatest advances in EDA. It accomplishes this in the form of technical papers, talks, company booths, product pavilions and panel discussions.

A key aspect … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center