Although much of the EDA industry has consolidated into the “Big 3” players, there are still plenty of smaller vendors in the market. In the earlier days of EDA, it seemed that most startups existed only until they failed or did well enough to be acquired. The industry has changed; there are now a number of notable companies that have existed independently for years, growing and thriving. Maybe they’ll be acquired someday, or maybe they’ll go public when times are better, but for now they’re doing just fine on their own. Agnisys is one of these successful companies, and to learn more about them I had a chat with CEO and founder Anupam Bakshi.

Although much of the EDA industry has consolidated into the “Big 3” players, there are still plenty of smaller vendors in the market. In the earlier days of EDA, it seemed that most startups existed only until they failed or did well enough to be acquired. The industry has changed; there are now a number of notable companies that have existed independently for years, growing and thriving. Maybe they’ll be acquired someday, or maybe they’ll go public when times are better, but for now they’re doing just fine on their own. Agnisys is one of these successful companies, and to learn more about them I had a chat with CEO and founder Anupam Bakshi.

Who is Agnisys?

We’re an EDA company dedicated to solving complex design and verification problems for system development. We believe in a specification-driven development flow for registers and sequences in system-on-chip (SoC) and IP projects, and our products enable this flow. Our goal is to enable faster design, verification, firmware creation, and validation. Our products increase the productivity of individual engineers and projects teams, while producing better designs and verification environments by eliminating common errors.

What is your background?

I received both a BSc Electronics and an MSc Electronics from Delhi University in India. My early career focused on EDA, developing internal tools for several companies and working at Gateway Design Automation, the creator of Verilog, and Cadence. Along the way, I earned an MS in Computer Engineering and a High-Tech MBA from Northeastern University. I did some consulting work and led a verification team at Avid Technology before the entrepreneurial bug bit me and I founded Agnisys. That was in 2007, and we just celebrated our thirteenth anniversary as an independent company. It’s been a fun and challenging journey!

What customer issues do you address?

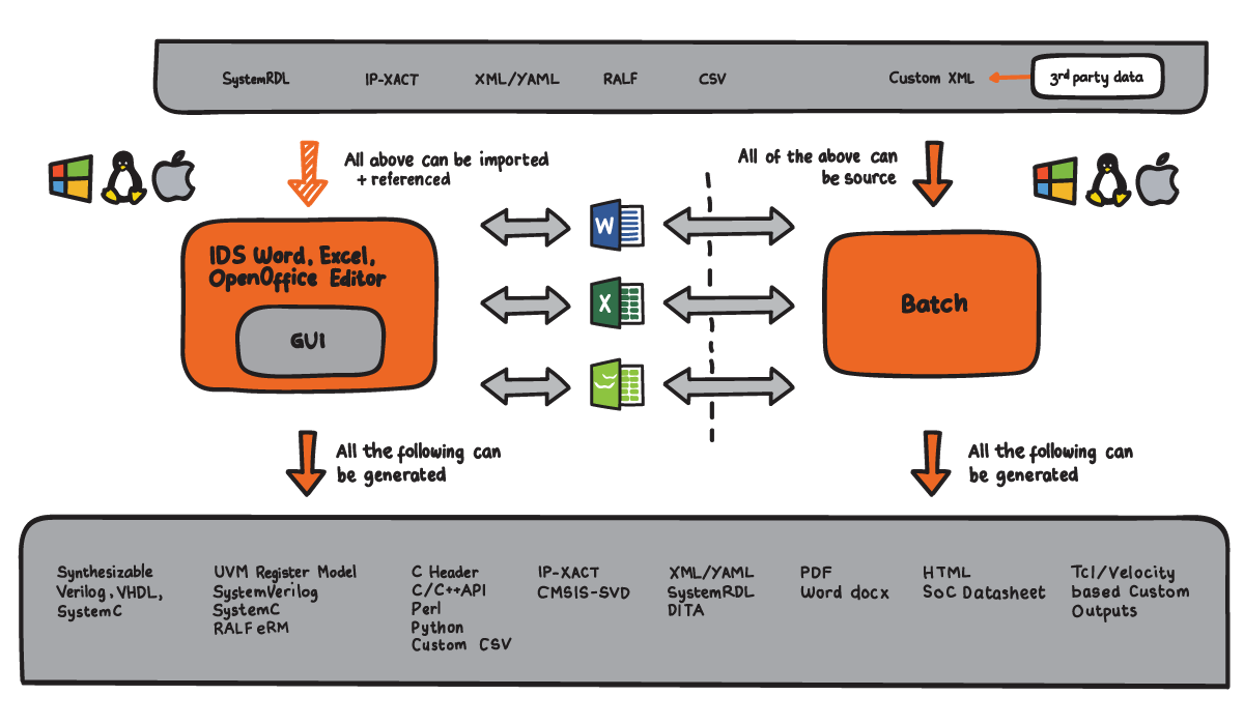

I started Agnisys to help solve some of the problems I faced first-hand in my previous roles. Chips keep getting bigger, and verification gets even harder. The only way for engineers to tackle this growth is to automate more of their development process. We started with IDesignSpec™ (IDS), which enables engineers to create an executable specification for registers and automatically generate outputs for software and hardware teams. The input specification can be in an industry-standard format such as SystemRDL or IP-XACT, or it can be created interactively by using a plug-in for Microsoft Word or Excel. IDS produces all sorts of outputs, including synthesizable Verilog and VHDL RTL, UVM models, C, Word, HTML, and other formats. Automatic generation saves project engineers weeks or months of time while eliminating the inevitable errors in hand-written code.

Are you an IP company as well as an EDA vendor?

That’s a really good point. We usually don’t describe ourselves that way, but we do generate IP. The RTL becomes part of the chip design, the UVM models become part of the testbench, the C headers are used in diagnostic and device driver programs, and the Word and HTML files are incorporated into the chip documentation.

Do you have other products available?

We have extended register automation in two major directions. Automatic Register Verification (ARV™) is an add-on to IDesignSpec for automatically verifying and validating all registers, including complex types. ARV generates the complete UVM testbench: bus agents, monitors, drivers, adaptors, predictors, sequencers, and sequences, plus a makefile and a verification plan. It generates assertions for formal tools. It can also generate tests for a variety of platforms including bare-metal hybrid C-UVM platforms. The generated files support both popular industry simulators and formal verification tools.

We have also expanded beyond registers to generate sequences for IP blocks such as bus interfaces. ISequenceSpec™ (ISS) enables users to describe the configuration, programming, and test sequences of an IP and automatically generate programming and test sequences ready to use. ISS generates UVM sequences for verification, C code for firmware and device driver development, CSV for Automatic Test Equipment (ATE) post-silicon validation, and more.

What’s new at Agnisys?

There’s a lot new, actually. At this year’s virtual Design Automation Conference (DAC), we announced general availability of three major new products that have been in development and use by early adopters for some time. You pointed out that we are also an IP provider, and we’ve moved more in this direction with our new SLIP-G™ (Standard Library of IP Generators). We offer an interface for IP customization and configuration, and generate the design RTL, the UVM testbench models, and the programming sequences. We have GPIO, I2C, timer, and programmable interrupt controller (PIC) IP available today, and we expect the library to grow over time based upon customer demand.

Assembling the SLIP-G IP and other blocks into an SoC is a huge challenge. Chips may have 500 or more major blocks and tens of thousands of connections among them. We developed SoC Enterprise™ (SoC-E) to be a flexible and customizable environment for design assembly of the most complex chips. We have made even more IP available; SoC-E can generate RTL aggregators, bridges, and multiplexors as needed by the SoC architecture. SoC-E’s Smart Assembler technology automatically integrates and connects these blocks, SLIP-G IP, IP from other sources, and user blocks into a complete SoC.

Finally, at DAC we announced IDS NextGen™ (IDS-NG), a specialized integrated development environment (IDE) for large IP blocks and SoCs. It provides a sophisticated GUI for capturing register and sequence specifications. We’ve made it available on Windows, Linux, and MAC platforms for maximum usability. It serves as a common front end for IDS, ARV, ISS, and SoC-E, enabling the fully automated flow of registers and sequences that we’ve envisioned for years. IDS-NG will help all users increase their efficiency, improve their design and verification quality, reduce project costs, and minimize time to market.

I read that Agnisys has taken the Open COVID Pledge; what is that?

We have joined a group of companies who have pledged free IP to help fight the deadly pandemic. Specifically, we make our tools and generated IP available for free to any engineers designing chips for medical applications in the research, diagnosis, or treatment of COVID-19. We really hope that we can help enable some real solutions.

Where are you located and who are your customers?

We’re headquartered in Boston, Massachusetts, with R&D centers and application engineers in the United States and India. Agnisys is a privately held company, self-funded and profitable thanks to the quality of our products and our outstanding customer service. We have customers located around the world, with a partial list at https://www.agnisys.com/agnisys-customer/.

Where can readers learn more?

Please visit our website at http://www.agnisys.com/.

Also Read:

Interview with Altair CTO Sam Mahalingam

CEO Interview: John O’Donnel of yieldHUB

CEO Interview: Deepak Kumar Tala of SmartDV

Share this post via:

Solving the EDA tool fragmentation crisis