Last month at DAC I met up with Michael Munsey of Methodics to get a quick update on what has been happening over the past 12 months within his company, and he quickly invited me to watch an archived webinar on their latest tool for IP Lifecycle Management called Percipient. I love to play the board game Scrabble, so i had to Google the … Read More

High Density Advanced Packaging Trends

Thursdays at the Design Automation Conference (DAC) are always a good time to catch up on areas of technology which are adjacent to that which you normally work. The exhibit floor is over and you have more time to spend in seminars. At this year’s DAC, I took advantage of a half day seminar put on by Mentor, a Siemens business, … Read More

Applying ISO 26262 in a Fabless Ecosystem – DAC Panel Discussion

The fabless movement was instrumental in disaggregating the semiconductor industry. Vertical product development at the chip and system level has given way to a horizontal structure over the years. This organization of product development has been doing an admirable job of delivering extremely reliable products. However… Read More

HLS update from Mentor about Catapult

I recall back in the late 1980’s when logic synthesis tools were first commercialized, at first they could read in a gate-level netlist from one foundry then output an optimized netlist back into the same foundry. Next, they could migrate your gate-level netlist from Vendor A over to Vendor B, giving design companies some… Read More

Cadence’s Tempus – New Hierarchical Approach for Static Timing Analysis

While at the 54[SUP]th[/SUP] Design Automation Conference (DAC) I had the opportunity to talk with Ruben Molina, Product Management Director for Cadence’s Tempus static timing analysis (STA) tool. This was a good review of how the state-of-the-art for STA has evolved over the last couple decades. While the basic problem hasn’t… Read More

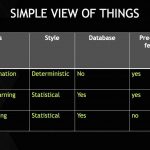

Machine Learning in EDA Flows – Solido DAC Panel

At DAC this year you could learn a lot about hardware design for AI or Machine Learning (ML) applications. We are all familiar with the massively parallel hardware being developed for autonomous vehicles, cloud computing, search engines and the like. This includes, for instance, hardware from Nvidia and others that enable ML … Read More

Designing at 7nm with ARM, MediaTek, Renesas, Cadence and TSMC

The bleeding edge of SoC design was on full display last month at DAC in Austin as I listened to a panel session where members talked about their specific experiences so far designing with the 7nm process node. Jim Hogan was the moderator and the panel quickly got into what their respective companies are doing with 7nm technology already.… Read More

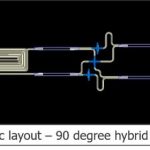

Mentor & Phoenix Software Shed Light on Integrated Photonics Design Rule Checking

Just prior to the opening of the 54[SUP]th[/SUP] Design Automation Conference, Mentor, a Siemens company, and PhoeniX Software issued a press release announcing a new integration between their tools to help designers of photonic ICs (PICs) to close the loop for manufacturing sign-off verification. This is a significant piece… Read More

Cadence Explores Smarter Verification

Verification as an effectively unbounded problem will always stir debate on ways to improve. A natural response is to put heavy emphasis on making existing methods faster and more seamless. That’s certainly part of continuous improvement but sometimes we also need to step back and ask the bigger questions – what is sufficient … Read More

Embedded FPGA’s create new IP category

FPGA’s are the new superstar in the world of Machine Learning and Cloud Computing, and with new methods of implementing them in SOC’s there will be even more growth ahead. FPGA’s started out as a cost effective method for implementing logic without having to spin an ASIC or gate array. With the advent of the web and high performance… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry