IC designers using advanced nodes are acutely aware of how variation effects in the silicon itself are causing increased analysis and design efforts in order to yield chips at acceptable levels. Four authors from Solidoare so passionate about this topic that they combined their years of experience into a book that I had a chance… Read More

Electronic Design Automation

Sequential Power Optimization

Calypto has an interesting webinar coming up about Minimizing RTL Power Through Sequential Analysis. It is next Tuesday December 4th at 11am.

Insert standard paragraph about how power is the new timing, everyone worries about power, battery life in smartphones, half-empty datacenters.

You probably already know about clock… Read More

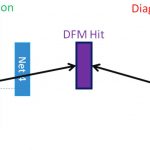

GLOBALFOUNDRIES and Mentor Develop Methods to Identify Critical Features in IC Designs

Since the beginning of the semiconductor industry, improving the rate of yield learning has been a critical factor in the success silicon manufacturing. Each fab has dedicated yield teams that look at the yield of wafers manufactured the previous day and attempt to find the root cause of any unexpected “excursions.” In earlier… Read More

AMS IC Design at Rohde & Schwarz

I met Frank Wiedmann on LinkedIn because we are both members of the Analog Mixed Signal group, and he has an interesting background in AMS IC design.

Since he lives in Munich we conducted our interview by email.… Read More

Give me a pair of wires, I’ll give you Ethernet in cars

A very astute gentleman said to me a few years ago that he’d seen a lot of networking technology come and go – Token Ring, FDDI, Fibre Channel, InfiniBand – but the only one that held up over time was Ethernet.… Read More

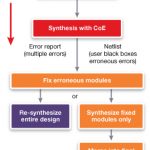

Second FPGA to the right, and straight on ‘til it works

In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there … Read More

ASIC Prototyping: Dini Group and Tektronix

Collaboration in EDA is nothing new, however you may not be aware of how the Dini Group and Tektronix have worked together on an FPGA prototyping platform to address issues like debugging with full visibility across an entire multi-FPGA design. At SemiWiki we’ve blogged a couple of times so far about the new debug approach… Read More

Tanner EDA Tops 1,200 Active Customers!

It is always nice to see when an EDA company grows organically, versus inorganically by acquiring friends and foes. It is also nice to see when an EDA company invests in the fabless semiconductor ecosystem because, as we know, we are all in this together.

Tanner EDA celebrated its 25th anniversary this year by adding 149 new customers… Read More

Apache on Signal Integrity

Matt Elmore has a two-part blog about the growing complexity of signal integrity analysis, both on the chip itself and the increasingly complex analysis required to make sure that signals (and power) get in and out of the chip from the board cleanly, especially to memory, which requires simultaneous analysis of chip-package-system… Read More

EDS Fair: Dateline Yohohama

Electronic Design and Solutions Fair (EDSF) was held in Yokohama Japan from Wednesday to Friday last week. It was held at the Pacifico Hotel, somewhere I have stayed several times, not far from the Yokohama branch of Hard Rock Cafe and, what used to be at least, the biggest ferris-wheel in the world.

Atrenta was one of the many companies… Read More

Quantum Computing Technologies and Challenges