OEM agreements don’t seem to work in EDA. Sometimes they are signed but usually they turn out to be closer to joint marketing agreements. The reason seems to be that EDA software is complex and requires high-touch support especially when getting the product first installed and introduced into a production flow. The effect… Read More

Electronic Design Automation

Designing for Variation

There is a widespread phenomenon in designing chips that new effects creep up on you. First they are so small you can ignore them. Then you can add a little pessimism to your timing budget or whatever gets affected. But eventually the effects go from second order to first order. You certainly can’t ignore them, and the guard … Read More

GaN Technology for the Connected Car

GaN technology is disruptive, in the best sense of the word, making possible what was once thought to be impossible – eGaN® technology is 10 times faster, significantly smaller, and with higher performance at costs comparable to silicon-based MOSFETs. The inevitability of GaN displacing the aging power MOSFET is becoming clearer… Read More

My Candid Conversation with Karen Bartleson

If you don’t know about Karen Bartleson, before I get into details, let me tell you that she was the President of IEEE-SA for the past 2 years and has been nominated by the IEEE Board of Directors as one of the candidates for IEEE President-Elect for 2016. The IEEE is an organization I admire as it plays a key role in advancing technology… Read More

Snapdragon 820 SoC Finds Qualcomm at Crossroads

Qualcomm’s new system-on-chip (SoC), Snapdragon 820, has come out with a few technical details, and it’s already making waves with its impressive GPU features and a powerful camera engine. At the same time, however, a couple of industry bytes have clouded the Snapdragon 820 launch fanfare.

First, Apple’s… Read More

DVCon India

After its successful launch last year, the “Design and Verification Conference & Exhibition India” (DVCon India) will be held on Sept 10 – 11 in Bangalore. The event primarily has two tracks: ESL and DV. The ESL track covers electronic system level (ESL) design and verification, including virtual prototypes of electronic… Read More

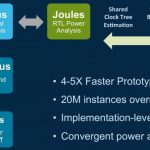

A New Unified Power Solution at All Levels

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

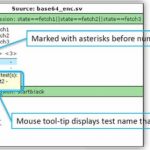

Aldec updates two EDA product lines

Continuous, incremental improvement based on customer feedback and insight from researchers is a pillar of the Aldec EDA strategy. Within the last two weeks, two of the Aldec product lines – Riviera-PRO, and ALINT-PRO-CDC – have seen new version releases. Here’s a quick look at some of the highlights of both.

Riviera-PRO 2015.06… Read More

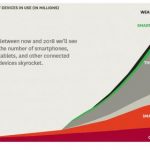

Meeting Demand as Fab Capacity is Stretched Again

Global semiconductor production capacity and its utilization level are key elements of the technology economy. During a panel at DAC in June Mentor Graphics posited that we are entering into a period where leading edge processes will be in high demand and also older nodes are seeing increasing demand due to Internet of Things designs… Read More

Design For Safety in Automotive Electronics

Do you remember how auto maker Toyota had to pay a $1.2 billion settlement in 2014 because some of their automotive models experienced sudden, unintended acceleration? That scenario has to be an engineer’s worst nightmare because something was missed during the design and testing of an automotive electronics system that… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center