I was kind of shocked when the service manager at our local VW dealership told me that one of the wires in the ignition system of my wife’s New Beetle had started to overheat, melting the insulation and becoming a safety hazard. Why didn’t a fuze just blow, protecting the wiring from overheating? We decided to quickly … Read More

Electronic Design Automation

Palladium Moves Power (and Temperature) Modeling to the System Level

I had a debate with Steve Carlson of Cadence earlier in the year at the EDPS conference on whether there were really any truly effective solutions for doing power estimation in emulation. I thought there weren’t and he said I was wrong. After attending the Cadence front-end summit last week, I have to admit he has a point.

First, who… Read More

3 flavors of TMR for FPGA protection

Back in the microprocessor stone age, government procurement agencies fell in love with the idea of radiation hardened parts that might survive catastrophic events. In those days, before rad-hard versions of PowerPC and SPARC arrived, there were few choices for processors in defense and space programs.

One of the first rad-hard… Read More

Does Managing Tools as if they are IP Make Sense?

Years ago I thought that chip design companies would embrace the latest technology and be eager to adopt new tools. What I learned was that the people implementing and managing design projects were taking a lot of risks with almost every aspect of their projects. What they most wanted is to minimize risk from the design process – especially… Read More

5 Verification Challenges of IoT Solved by Emulation

Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which… Read More

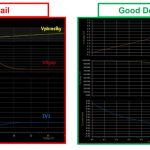

Cadence Enters the RTL Power Estimation Game

At the Cadence front-end summit last week, Jay Roy presented the Cadence Joules solution for RTL (and gate-level) power estimation. Jay is ex-Apache, so knows his way around RTL power estimation which should make Joules a product to watch. Joules connects very natively to Palladium for power characterization for realistic software… Read More

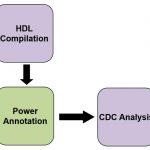

Syncing Up CDC Signals in Low Power Designs

So far in my blog series on low power we’ve looked broadly at what’s changing in the low power verification landscape and focused on a new methodology developed by Mentor Graphics and ARM called successive refinement, which is now included in the UPF standard. Power management techniques create their own brand of clock domain crossing… Read More

Optimizing power for wearables

I was at the Cadence front-end summit this week; good conference with lots of interesting information. I’ll start with a panel on optimizing power for wearables. Panelists were Anthony Hill from TI, Fred Jen from Qualcomm, Leah Clark from Broadcom and Jay Roy from Cadence. Panels are generally most entertaining when the panelists… Read More

IDMs are Much Ahead of Fabless Semicon Companies

In a balancing global economy, it’s a common phenomenon that at certain times a few sectors or segments within the sectors grow much faster compared to others. And a few companies within the growing sectors lead those sectors. Both the growing sectors and the leading companies in those sectors become the centers of attraction. … Read More

Design and Optimization of Analog IP is Possible

Designing Analog IP is often referred to as a “black art”, something that only highly experienced craftsmen can produce using transistor-level techniques that aren’t shared outside of their closely held group of trusted co-workers. I’d like to suggest that Analog IP can be designed and optimized … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center