When the topic of hardware emulation comes up, thoughts of big iron customarily come to mind. However, hardware emulation has evolved significantly and now there are other important traits that distinguish the offerings in this area. For a very long period of time emulators provided primarily a method to accelerate gate level… Read More

Electronic Design Automation

Aldec reprograms HES7 for AXI4 speed

FPGA-based prototyping firms are all grappling with the problem of higher speed connectivity between a development host and their hardware. Aldec is announcing their solution at DVCon 2016, turning to an AMBA AXI4 interface bridged into a host with PCIe x8.

Faster host interfaces deliver dual benefits in FPGA-based prototyping.… Read More

HW/SW Interfaces for Portable Stimulus

With growing size and complexity of SoC, the semiconductor community is realizing the growing pain of verification. The cost of SoC verification grows exponentially with design size. Moreover, there is no single methodology for verifying a SoC; multiple engines are used in different contexts through different verification… Read More

Design Verification Challenges: Past, Present and Future!

Next week I will be at DVCON which is not to be confused with DEFCON the community of black and white hat hackers that challenge our online privacy on a daily basis. DVCON is the premier conference for the functional design and verification of our beloved electronic devices. The big draw next week of course is the keynote by Dr. Walden… Read More

Mentor ARM subscription signals ecosystem shift

Since creating the landmark “all-you-can-eat” license with Samsung in 2002, ARM has inked several subscription deals with chipmakers and EDA firms. The latest ARM subscriber license deal just announced is for Mentor Graphics. What makes their strategy unique?… Read More

Sustainability, Semiconductor Companies and Software Companies

I certainly want to leave the Earth a better place to live for my children and generations to come, so sustainability is a value that resonates with me. How is a consumer like me to know which companies are the most sustainable in areas that matter, like:… Read More

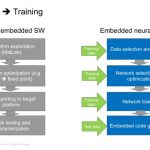

Neural Networks Ready for Embedded Platforms

If you are not yet familiar with the term Convolutional Neural Networks, or CNN for short, you are certainly bound to become in the year ahead. Using Artificial Intelligence in the form of CNN is on the verge of replacing a large number of computing tasks, especially those involving recognizing things such as sounds, shapes, objects,… Read More

S2C opens up FPGA prototyping for PCIe fabrics

Reconfigurable computing began with FPGA cards dropped into expansion slots in workstations. FPGA-based prototyping vendors tended away from that model as interconnect speeds rose and cabling complexity between modules increased. Much faster PCIe interfacing and bigger FPGAs mean revisiting the concept.… Read More

Synopsys at DVCon 2016

It’s that time of year again – DVCon starts on Monday Feb 29[SUP]th[/SUP] and as always should be a packed event. Synopsys plans a big showing, in the exhibit hall, in a sponsored lunch, at tutorials and in papers. Time to get your conference shoes on and go check them out – I plan to be there all week.

One of the most obvious things you will… Read More

A Brief History of Open-Silicon

In 2003, when Open-Silicon was founded there was a growing need for flexible and innovative ways of getting chip designs manufactured. Semiconductor companies, given the alternatives of COT or traditional ASIC, often were looking for more flexibility without the huge investment and risk of going COT. Let’s look at how Open-Silicon… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center