In the 35 years since commercial EDA went mainstream a lot of advances have been made but the fundamental architecture and even the philosophy of tooling have really not advanced at all. Tools are designed around individual tasks – analysis and optimization within a specific domain – under the assumption that variability within… Read More

Electronic Design Automation

Google TPU Another Step in a Shifting Semiconductor Landscape

Markets work when consumers of a widget don’t feel there is significant differentiated value in making their own and would rather get lowest possible cost from experienced widget makers who can amortize their investment over high-volume sales to many customers. But that changes when a large consumer finds they can increase differentiated… Read More

Where are the Entrepreneurs?

This week I attended the UpWest Labs event in San Francisco. UpWest Labs provides seed funding and incubation for a wide range of domains including Enterprise Software, Internet of Things, Infrastructure Technologies, Artificial Intelligence, Consumer Applications, Drones, Cyber Security, Augmented Reality / Virtual … Read More

Aldec extends FPGA and ASIC flows at DAC

Aldec tools and services have long been associated with FPGA designs. As FPGAs have evolved toward more RTL-based designs, the similarities between a modern FPGA verification flow and an ASIC verification flow often leave them looking virtually the same. … Read More

Stop FinFET Design Variation @ #53DAC and get a free book!

If you plan on visiting Solido (the world leader in EDA software for variation-aware design of integrated circuits) at the Design Automation Conference next month for a demonstration of Variation Designer, register online now and get an autographed copy of “Mobile Unleashed”. Such a deal!

Solido Variation Designer is used by… Read More

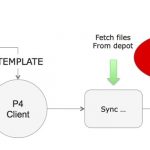

Bulking Up of Design Data Calls for Version Control on Steroids

Even though design management systems are gaining popularity as a way to manage design data growth, they actually contribute to the problem of exploding data size. What we already know is that a linear increase in die size causes exponential growth in chip area, and that smaller feature sizes compound this effect in the same way.… Read More

Army of Engineers on Site Only Masks Weakness

Hardware emulation was conceived in the 1980s to address a design verification crisis looming on the horizon. In those days, the largest digital designs were stressing the limits of the software-based, gate-level simulator that was the mainstream tool for the task.

It was anticipated and confirmed in short notice that adopting… Read More

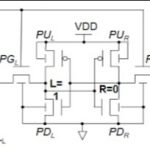

SRAM Optimization for 14nm and 28nm FDSOI

I’ve done SRAM and DRAM design before as a circuit designer from 1978-1986, but in 2016 there are so many more challenges to using 28nm and 14nm on FDSOI technology. One way to keep abreast of SRAM design is to read conference papers, so I just finished a paper from authors at STMicroelectronics and MunEDA presented at the IEEE… Read More

DAC 2016 – Register Now

DAC is again going to be in Austin (reason enough to go), from June 6[SUP]th[/SUP]-8[SUP]th[/SUP] for the main event. A number of events caught my eye:

- Monday AM – custom hardware for algorithmic trading. If you want to know more about FinTech (technology for finance) this could be for you

- Another Monday morning session on Linux

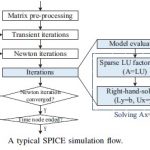

The Emerging Importance of Parallel SPICE

SPICE simulation is the workhorse tool for custom circuit timing validation and electrical analysis. As the complexity of blocks and macros has increased in advanced process nodes — especially with post-layout extraction parasitic elements annotated to the circuit netlist — the model size and simulation throughput… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center