I attended a Mentor verification seminar earlier in the year at which Russ Klein presented a fascinating story about a real customer challenge in debugging a power problem in a design around an ARM cluster. Here’s the story in Russ’ own words. If you’re allergic to marketing stories, read it anyway. You might… Read More

Electronic Design Automation

Solving a Murder Case with IoT Devices

I watch a lot of Netflix and there are so many detective movies and series for me to enjoy where I try and match wits with the bad guys and figure out who is guilty a few seconds before the law enforcement characters do. On TV and with our movies there is often critical evidence extracted from desktop computers, laptops, hard drives, smart… Read More

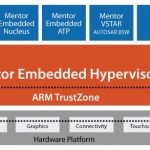

Real Time Virtualization, How Hard Can it Be?

My first exposure to running something virtual on a computer was when I decided to run the Windows OS on my MacBook Pro using software provided by Parallels. With that virtualization I was able to run the Quicken app under Windows on my MacBook Pro, along with the popular Internet Explorer web browser. The app performance on virtualized… Read More

NetSpeed Leverages Machine Learning for Automotive IC End-to-End QoS Solutions

A couple of weeks back I wrote an article about the use of machine learning and deep neural networks in self-driving cars. Now I find that machine learning is also being applied to help build advanced end-to-end QoS (quality of service) solutions for the automotive IC market. With the advent of self-driving cars comes requirements… Read More

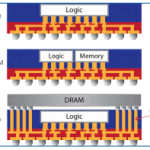

Moving from SRAM to DDR DRAM in Safety Critical Automotive Systems

Until now, most of the processors contained within automobiles could be served by SRAM, at the exception of infotainment systems relying on a more powerful CPU connected to DRAM, but these systems are non-safety-critical. Advanced Driver Awareness Systems (ADAS) and self-driving vehicle systems demand powerful processors… Read More

Building a Virtual Prototype

I wrote recently about how virtual prototypes (in the form of VDKs) can help embedded software teams practice continuous integration. Synopsys has just released a white paper detailing a practical approach to building a VDK, using the Juno ARM development platform (ADP) to illustrate. Just as a reminder, the point of a virtual… Read More

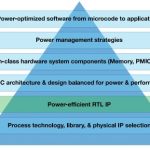

How ARM designs and optimizes SoCs for low-power

ARM has become such a worldwide powerhouse in delivering processors to the semiconductor IP market because they have done so many things well: IP licensing model, variety, performance, and low-power. On my desk are two devices with ARM IP, a Samsung Galaxy Note 4 smart phone and a Google tablet. Most of my readers will likely have… Read More

CEO Interview: Dündar Dumlugöl of Magwel

Magwel CEO Dündar Dumlugöl is well known from his days at Cadence, where I first met him, and for his more recent tenure at Magwel. At Cadence he led the team that first developed Spectre. He has come a long way from the start of his career at IMEC in Belgium. He and I had a chance to have a conversation recently where he offered insights … Read More

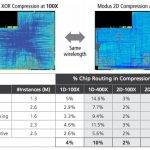

Reducing the Cost of SoC Testing

Every year certain technology themes appear, like at ITC this year a big theme was how to reduce the cost of SoC testing. I spoke with Rob Knoth of Cadence by phone to hear more about this cost of test theme. Rob gave me an example of an SoC that takes 27 seconds on a tester, so at $0.04 per second in test costs amounts to $1.08 per part. If you… Read More

Design for Fanout Packaging

In constant pursuit of improved performance, power and cost, chip and system designers always want to integrate more functions together because this minimizes inter-device loads (affecting performance and power) and bill of materials on the board (affecting cost). However it generally isn’t possible to integrate … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center