This. AI in PCB design is not a new idea. Other PCB software companies also make that claim. But when a mainstream systems technology company like Siemens talks about the subject, that is noteworthy. They already have an adaptive user interface (UI) for their mechanical modeling suite and to assist in low-code development for application… Read More

Artificial Intelligence

Webinar: Flexible, Scalable Interconnect for AI HW System Architectures

Building next generation systems is a real balancing act. The high-performance computing demands presented by increasing AI an ML content in systems means there are increasing challenges for power consumption, thermal load, and the never-ending appetite for faster data communications. Power, performance, and cooling … Read More

Pushing Acceleration to the Edge

As more AI applications turn to edge computing to reduce latencies, the need for more computational performance at the edge continues to increase. However, commodity compute engines don’t have enough compute power or are too power-hungry to meet the needs of edge systems. Thus, when designing AI accelerators for the edge, Joe… Read More

Quadric’s Chimera GPNPU IP Blends NPU and DSP to Create a New Category of Hybrid SoC Processor

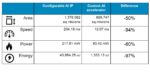

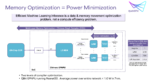

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

New Cadence Joint Enterprise Data and AI Platform Dramatically Accelerates AI-Driven Chip Design Development

Without data, there is no computing field to talk about, no technology world to awe at and not much of a semiconductor industry to work in. There is no argument that data is the foundational piece for everything, has been to date and will continue to be. While processing an application’s input data is essential to serve the intended… Read More

Test Ordering for Agile. Innovation in Verification

Can we order regression tests for continuous integration (CI) flows, minimizing time between code commits and feedback on failures? Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas.… Read More

Arm and Arteris Partner on Automotive

Whenever a new partnership is announced, the natural question is, “why?” What will this partnership make possible that wasn’t already possible with those two companies working independently? I talked yesterday with Frank Schirrmeister of Arteris on the partnership. (Yes, Frank is now at Arteris). And I just got off an Arm press… Read More

Semifore is Supplying Pain Relief for Some World-Changing Applications

In a recent post, I discussed how Samtec is fueling the AI revolution. In that post, I talked about how smart everything seems to be everywhere, changing the way we work, the way we think about our health and ultimately improving life on the planet. These are lofty statements, but the evidence is growing that the newest wave of applications… Read More

Flex Logix: Industry’s First AI Integrated Mini-ITX based System

As the market for edge processing is growing, the performance, power and cost requirements of these applications are getting increasingly demanding. These applications have to work on instant data and make decisions in real time at the user end. The applications span the consumer, commercial and industrial market segments.… Read More

Finally, A Serious Attack on Debug Productivity

Verification technologies have progressed in almost all domains over the years. We’re now substantially more productive in creating tests for block, SoC and hybrid software/hardware verification. These tests provide better coverage through randomization and formal modeling. And verification engines are faster – substantially… Read More

Siemens U2U 3D IC Design and Verification Panel