Designing SOC’s for markets like automotive and mobile electronics requires taking advantage of every opportunity for optimization. One way to do this is through building a cache coherent system to boost speed and reduce power. Recently, NXP decided to go about this on their automotive MCU based SOC’s by using Arteris’ just-announced… Read More

Author: Tom Simon

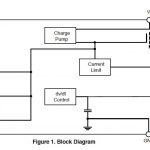

Who protects power protection chips?

Power protection chips are widely used these days to protect sensitive circuitry from over-voltage and over-current stress. However, these workhorse chips are often subjected to extraordinary thermal stress themselves and need to be protected from burning up – literally.

Power protection chips work like electronic fuses,… Read More

Cache Coherent Systems Get a Boost from New Technology

The speed and power penalties for accessing system RAM affect everything from artificial intelligence platforms to IoT sensor nodes. There is a huge power and performance overhead when the various IP blocks in an SOC need to go to DRAM. Memory caches have become essential to SOC design to reduce these adverse effects. However, … Read More

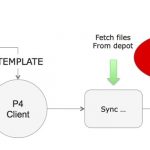

Bulking Up of Design Data Calls for Version Control on Steroids

Even though design management systems are gaining popularity as a way to manage design data growth, they actually contribute to the problem of exploding data size. What we already know is that a linear increase in die size causes exponential growth in chip area, and that smaller feature sizes compound this effect in the same way.… Read More

How to Deal With Seven Design Closure Issues

The challenge of tracking design progress is a shared problem for individual designers, team leaders, and project managers. At each level the ability to step back from just reviewing error log files and seeing the arc of the whole design as it moves forward is valuable. The difficulty of seeing the whole picture is exacerbated when… Read More

Making PLM Actually Work for for IC Design

The topic of Product Lifecycle Management (PLM) conjures up images of usage on airplanes, tanks and cars. That’s because it was developed decades ago to help make product development and delivery more efficient for big expensive manufactured products. It worked well for its intended markets by combining and managing all the … Read More

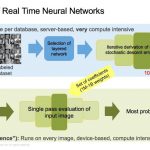

Neural Networks Poised to Make Big Changes in Our World

Probably the most interesting thing about Neural Networks is how they can be used for complex recognition tasks that we as people can easily perform but we might have a lot of trouble explaining how. One very good example of a problem that Neural Networks can tackle is determining when people are making a fake smile. Intuitively we… Read More

What SOC Size Growth Means for IP Management

Whether or not in the past you believed all the of rhetoric about exploding design complexity in SOC’s, today there can be no debate that SOC size and complexity is well beyond something that can be managed without some kind of design management system. As would be expected, development of most larger designs relies on a data management… Read More

Waze May Not Be So Evil After All

In contrast to the opinions in a recent article here, I think Waze is extremely beneficial to the individuals who use it, other drivers – by virtue of more efficient road usage, and the various jurisdictions that oversee roads and highways. For those not familiar with Waze, it is a smartphone app that provides navigation and… Read More

How HBM Will Change SOC Design

High Bandwidth Memory (HBM) promises to do for electronic product design what high-rise buildings did for cities. Up until now, electronic circuits have suffered from the equivalent of suburban sprawl. HBM is a radical transformation of memory architecture that will have huge ripple effects on how SOC based electronics are … Read More

Solving the EDA tool fragmentation crisis