No matter how high the processing capability of a chip, its overall performance is limited by IO speed. This is very similar to a car with low performance tires, a powerful engine will not be able to transfer its energy to the ground effectively. There is quite literally a race going on between core processing and IO speeds for transferring… Read More

Author: Tom Simon

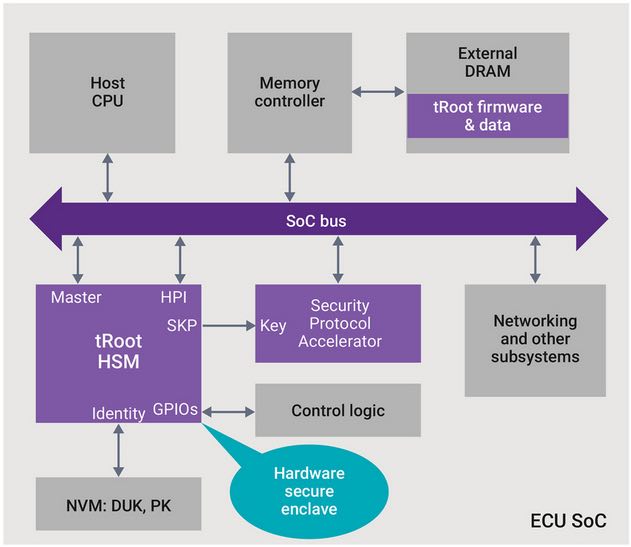

Car Vandals Eschew Crowbars

It used to be that automotive theft and crime was perpetrated with a crowbar. Now with increased electronics content, car designer and owners need to worry about electronic threats. Anywhere there is a communication link or a processor, there are potential threats to the security of the car. The range of these threats covers everything… Read More

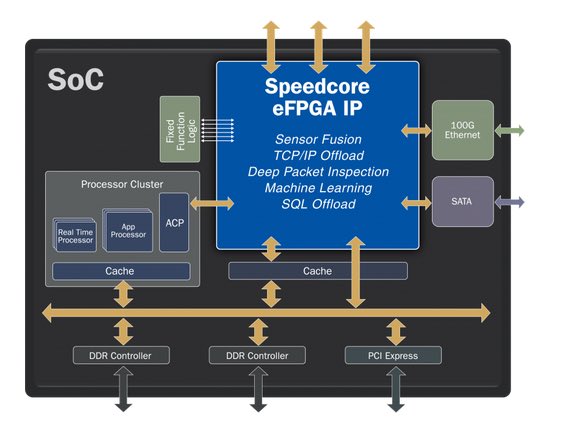

Achronix Assists Academics

In every semiconductor related field, innovation is the name of the game. Academic, non-profit and government research has been a consistent source of innovation. Look back at the US space program, basic science research and even military programs to see where much of the foundation of our current technological age came from.… Read More

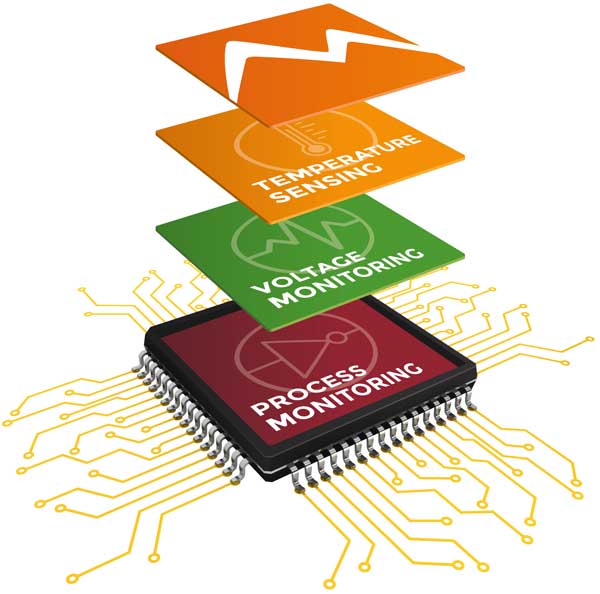

Making AI Silicon Smart with PVT Monitoring

PVT – depending on what field you are in those three letters may mean totally different things. In my undergraduate field of study, chemistry, PVT meant Pressure, Volume & Temperature. Many of you probably remember PV=nRT, the dreaded ideal gas law. However, anybody working in semiconductors knows that PVT stands … Read More

Eta Compute Receives Two Awards from ARM at TechCon

Many startups set out with the goal of accomplishing a technical feat that was previously considered impossible. Quite frankly most do not succeed. Yet, occasionally a company comes along that succeeds with a game changing breakthrough. ETA Compute has done just this. Yet, even more impressively, this 3-year-old company has… Read More

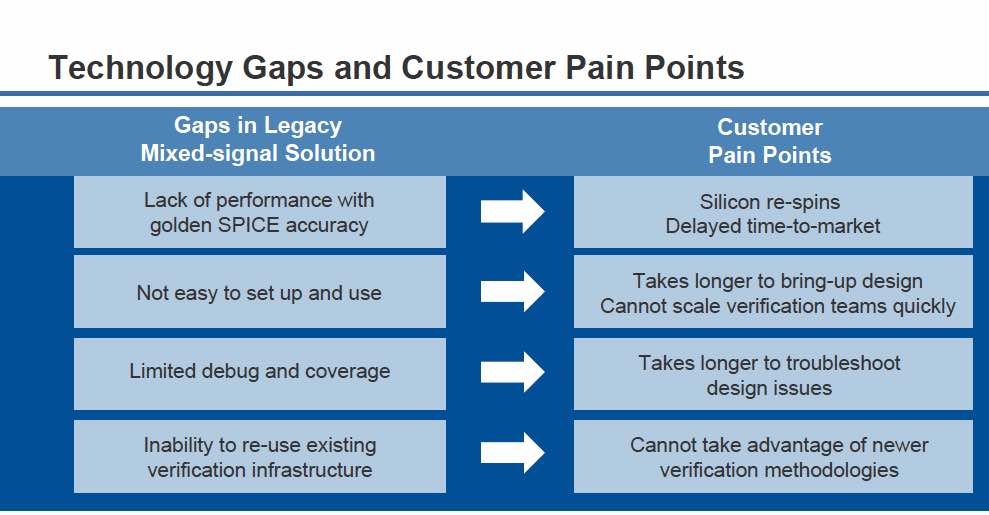

Mentor’s Symphony in Tune with AMS Designer Needs

Mixed signal simulation is a very hot topic these days. In modern designs, it is harder to draw a line between the analog and digital and work with them independently. Analog blocks are showing up everywhere. Even in what would have qualified as a digital design a few years ago, now designers need to look at things like PLLs, IOs and … Read More

IoT Security Process Variation to the Rescue

Unique device identities are at the core of all computer security systems. Just as important is that each unique identity cannot be copied, because once copied they can be used illegitimately. Unique device IDs are used to ensure that communications are directed to the correct device. And they also provide the ability to encrypt… Read More

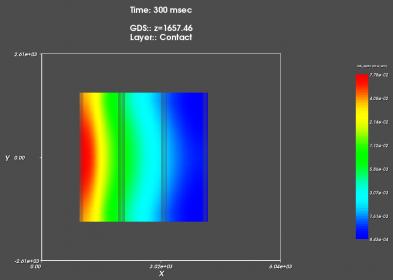

Coupled Electro-thermal Analysis Essential for PowerMOS Design

Power device designers know that when they see a deceptively simple pair of PowerMOS device symbols in the output stage of a power converter circuit schematic, they are actually looking at a massively complex network of silicon and metal interconnect. The corresponding physical devices can have a total device W on the order of … Read More

Open-Silicon Embraces the Latest ISO 9001 Specification with Certification by SGS

A quality standard that stays static and is not itself targeted for continuous improvement, is a standard that is breaking one of the first tenets of quality. This is why the ISO 9001 specification has been updated several times since its introduction in 1987. The first version was fairly modest. The most recent version was released… Read More

Mentor’s Busy ITC and Major Test Product Updates

In conjunction with the 2018 International Test Conference, Mentor has several interesting test announcements. They also have a busy round of technical activities, including a number of technical papers, presentations, tutorials and a poster from a major customer about using Mentor. I’d like to touch on the two product related… Read More

Breker Hosts an Energetic Panel on Spec-Driven Verification