You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

How should we assess the risk of harmful metastability in a clock domain crossing (CDC) when the semiconductor process has significant parameter variability? One possibility is to determine the MTBF of a synchronizer at the worst-case corner of the CDC. But that approach has some conflicting complications:

…

Read More

A Public Synchronizerby Jerry Cox on 02-09-2015 at 7:00 amCategories: EDA

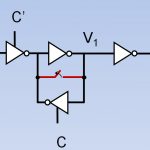

You might ask yourself “Why would anyone want to have a public synchronizer available to download?” Usually designers just grab a flip-flop from his or her company’s or a standard cell vendor’s library. However, are these handy solutions the best course of action today? Current SoC designs have numerous clock domains providing… Read More

Measuring Metastabilityby Jerry Cox on 01-24-2015 at 7:00 amCategories: EDA

Measuring metastability is just 50 years old this year. In 1965 my colleague Tom Chaney took a sampling ‘scope picture of an ECL flip-flop going metastable. S. Lubkin had made mention of the phenomenon over a decade before that, but at that time most engineers were unaware of the phenomenon or did not believe it actually existed. … Read More

The reliability metric, Mean Time Between Failures (MTBF), is often misunderstood. Use of an MTBF metric generally assumes a random failure process, one that is very infrequent and has no memory of past failures. Such failure modes can occur in System-on-Chip (SoC) designs and include radiation effects, synchronizer malfunctions… Read More

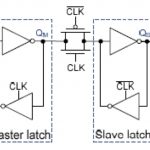

You may say, “Why should I worry about synchronizer failures when I have never seen one fail in a product?” Perhaps you feel that the dual-rank synchronizer used by many designers makes your design safe. Furthermore, those chips that have occasional unexpected failures never show any forensic evidence of synchronizer failures.… Read More

Estimating the MTBF of an SoC should always include an analysis of synchronizer reliability. Contemporary process nodes are introducing new challenges to the reliability of clock domain crossings so it is prudent to revisit how your simulation tool calculates a synchronizer’s MTBF. Let’s list the ten most common pitfalls.… Read More

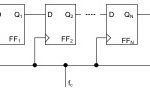

In Part 1 of this topic I discussed what it takes to estimate the mean time between failures (MTBF) of a single stage synchronizer. Because supply voltages are decreasing and transistor thresholds have been pushed up to minimize leakage, the shortened MTBF of many synchronizer circuits at nanoscale process nodes is presenting… Read More

Recently, I discussed the increasing risk of metastability hazards at nanoscale geometries. These risks are significantly aggravated at low supply voltages and low temperatures and must be addressed during the design cycle of any mission critical application. This time I discuss what it takes to estimate a synchronizer’s … Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior