ISTFA

Silicon Valley is a great location for trade shows and technical conferences, so if you have an interest in test and failure analysis then don’t miss out on the 37th annual International Symposium for Testing and Failure Analysis. This year ISTFA will be held from Sunday, November 13th thru Thursday, November 17th … Read More

Author: Daniel Payne

AMS Design using Dongbu HiTek foundry and Tanner EDA Tools

Every analog designer needs a foundry PDK (Process Design Kits) and EDA tools to design, layout and verify their AMS chip or IP. This week I had a chance to conduct an email interview with Taek-Soo Kim, VP of Technical Engineering at Dongbu HiTek in Korea. This specialty foundry supplies analog silicon worldwide.

Interview

Q: Tell… Read More

Oct 27 – Hands-on Workshop with Calibre: DRC, LVS, DFM, xRC, ERC (Fremont, California)

I’ve blogged about the Calibre family of IC design tools before:

Smart Fill replaced Dummy Fill Approach in a DFM Flow

Graphical DRC vs Text-based DRC

Getting Real time Calibre DRC Results with Custom IC Editing

Transistor-level Electrical Rule Checking

AMS Design at AnSem

AnSem has been in the AMS design business since 1998 and uses a variety of commercial EDA tools along with internally developed tools and scripts to automate the process of analog design and technology porting. Their IC designers have completed some 40 AMS projects in diverse areas like:

- RF CMOS

- LNA, VCO, Mixers

- Synthesizers

- Low-IF/Zero-IF

Mentor at the TSMC Open Innovation Platform Ecosystem Forum

EDA companies and foundries must closely collaborate in order to deliver IC tool flows that work without surprises at the 40nm and 28nm nodes.

Tomorrow in San Jose you can attend this 4th annual event hosted by TSMC along with Mentor Graphics and other EDA and IP companies.

Here are some of the topics that will interest IC designers… Read More

EDA and ITC

Every SOC that is designed must be tested and the premier conference for test is ITC, held last month in Anaheim, California.

I spoke with Robert Ruiz of Synopsys by phone on September 21st to get an update on what is new with EDA for test engineers this year. Robert and I first met back at Viewlogic when Sunrise was acquired in the 90’s.… Read More

FPGA Prototyping – What I learned at a Seminar

Intro

My first exposure to hardware prototyping was at Intel back in 1980 when the iAPX 432 chip-set group decided to build a TTL-based wire-wrap prototype of a 32 bit processor to execute the Ada language. The effort to create the prototype took much longer than expected and was only functional a few months before silicon came back.… Read More

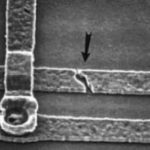

How ST-Ericsson Improved DFM Closure using SmartFill

DFM closure is a growing issue these days even at the 45nm node, and IC designers at ST-Ericsson have learned that transitioning from dummy fill to SmartFill has saved them time and improved their DFM score.

The SOC

ST-Ericsson designed an SOC for mobile platforms called the U8500 and their foundry choice was a 45nm node at STMicroelectronics… Read More

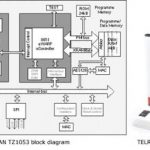

Circuit Simulation and Ultra low-power IC Design at Toumaz

I read about how Toumaz used the Analog Fast SPICE (AFS) tool from BDA and it sounded interesting so I setup a Skype call with Alan Wong in the UK last month to find out how they design their ultra low-power IC chips.

Interview

Q: Tell me about your IC design background.

A: I’ve been at Toumaz almost 8 years now and before that at Sony… Read More

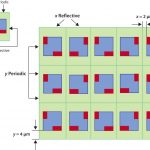

Memory Cell Characterization with a Fast 3D Field Solver

Memory designers need to predict the timing, current and power of their designs with high accuracy before tape-out to ensure that all the design goals will be met. Extracting the parasitic values from the IC layout and then running circuit simulation is a trusted methodology however the accuracy of the results ultimately depend… Read More

Application-Specific Lithography: Sense Amplifier and Sub-Wordline Driver Metal Patterning in DRAM