Apple announces their new products with much media attention to an audience of enthusiastic attendees, along with a live stream to all of us on the Internet who couldn’t be there in person. Samsung is following that same marketing playbook and today hosted an event in New York dubbed, “Everything Galaxy Unpacked 2015”… Read More

Author: Daniel Payne

Design For Safety in Automotive Electronics

Do you remember how auto maker Toyota had to pay a $1.2 billion settlement in 2014 because some of their automotive models experienced sudden, unintended acceleration? That scenario has to be an engineer’s worst nightmare because something was missed during the design and testing of an automotive electronics system that… Read More

Virtual Reality is Ready to Rocket

Virtual Reality (VR) is such a hot technology concept right now that the topic has made the cover of Time, Wired and Forbes magazines this year, along with countless online articles. What really captured my attention was that moment in 2014 when Facebook acquired VR startup Oculus for $2B, yes that is billions of dollars. The last… Read More

Talking Directly to EDA R&D

Many EDA companies keep their R&D engineers focused on product development and bug fixing, shielding them from any and all direct contact with end-users, mostly for fear of what might be revealed if such direct dialog were allowed. Customer support people are allowed to talk directly with customers, then pass along enhancement… Read More

Designing an IDCT for H.265 using High Level Synthesis

Math geeks know all about Inverse Discrete Cosine Transforms (IDCT) and a popular use is in the hardware architecture of High Efficiency Video Coding (HEVC), also known as H.265, the new video compression standard and widely used in consumer and industrial video devices. You could go about hand-coding RTL to create an IDCT function,… Read More

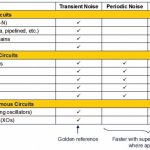

Device Noise Analysis, What Not to Do for AMS IC Designs

AMS IC designers have a lot to think about when crafting transistor-level designs to meet specifications and schedules, so the most-used tool in their kit is the trusted SPICE or FastSPICE circuit simulator to help analyze timing, power, sensitivity and even device noise. I just did a Google search for “device noise analysis… Read More

Choosing C++ or SystemC for High Level Synthesis

Most engineers learn by doing, and so at DAC in June an EDA vendor with High Level Synthesis (HLS) tools held a language tutorial on choosing C++ or SystemC for design and verification projects. The EDA company is Calypto, and Stuart Clubb put together the tutorial on using synthesizable C++ or SystemC. The design and verification… Read More

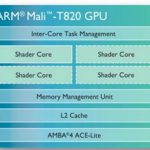

How ARM Implemented a Mali GPU using Logic Synthesis and Place/Route Tools

ARM is a well-known semiconductor IP provider and they often create a reference design so that SoC companies can have a starting point to work with. On the GPU side of IP the ARM engineers have an architecture called Mali, and a recent webinar hosted by Synopsys reviewed how the physical design area was minimized by using a combination… Read More

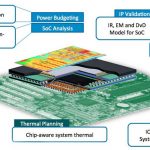

Benefits of RTL Power Budgeting

Only one company at the recent DAC conference and exhibit had a set of four interacting disciplines: Fluids, Structures, Electronics and Systems. Did you guess that the company was ANSYS? I get so IC focused at times that I almost forget that chips plug into boards, that boards become systems, and that systems drive and control mechanical… Read More

Tackling Layout Gradient Effects in 16 nm FinFET using Layout Automation

My first exposure to automating IC layout was back in the 1980’s at Intel where I coded a layout compiler to auto-generate about 6% of a graphics processor chip. The need to use automation for IC layout continues today, and with the advent of FinFET technology there are some new challenges like layout gradient effects that … Read More

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem