I love to read articles about autonomous vehicles and the eventual goal of reaching level 5, Full Automation, mostly because of the daunting engineering challenges in achieving this feat and all of the technology used in the process. The auto industry already has a defined safety requirements standard called ISO 26262, and one… Read More

Author: Daniel Payne

Formal Verification Approach Continues to Grow

After a few decades of watching formal verification techniques being applied to SoC designs, it certainly continues to be a growth market for EDA vendors. In the first decades from 1970-1990 the earliest forms of formal tools emerged at technical conferences, typically written by University students earning their Ph.D.s, … Read More

Webinar: System Level Modeling and Analysis of Processors and SoC Designs

Engineers love to optimize their designs, but that implies that there are models and stimulus to automate the process. Process engineers have TCAD tools, circuit designers have SPICE for circuit simulation, logic designers have gate-level simulators, RTL designers use logic simulation, but what is there for the system architects… Read More

Transistor-Level Static Checking for Better Performance and Reliability

My first transistor-level IC design job was with Intel, doing DRAM designs by shrinking the layout to a smaller process node, and it also required running lots of SPICE runs with manually extracted parasitics to verify that everything was operating OK, meeting the access time specifications and power requirements across PVT … Read More

Small EDA Company with Something New: SoC Compiler

I read the semiconductor press, LinkedIn and social media (Twitter, Facebook) every morning along with an RSS feed that I setup, staying current on everything related to using EDA tools to make the task of SoC design a bit easier for design teams. A recent press release announced a tool called SoC Compiler, so my curiosity was piqued… Read More

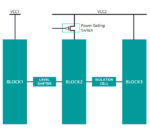

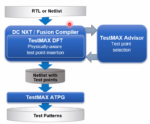

Addressing SoC Test Implementation Time and Costs

In business we all have heard the maxim, “Time is Money.” I learned this lesson early on in my semiconductor career when doing DRAM design, discovering that the packaging costs and time on the tester were actually higher than the fabrication costs. System companies like IBM were early adopters of Design For Test (DFT)… Read More

Single HW/SW Bill of Material (BoM) Benefits System Development

Most large electronics companies take a divide and conquer approach to projects, with clear division lines set between HW and SW engineers, so quite often the separate teams have distinct methodologies and ways to design, document, communicate and save a BoM. This division can lead to errors in the system development process,… Read More

A Brief History of Perforce

In 2020 Perforce acquired Methodics, a provider of IP Lifecycle Management (IPLM) tools, and Daniel Nenni blogged about that in July 2020, but a lot has happened since Perforce was founded in 1995. In the beginning Christopher Seiwald founded Perforce in his Alameda basement based on his background as a software developer, and… Read More

CES 2021 and all things Cycling Technology

It’s January so time to give you another summary of what I’ve found at CES 2021 about new cycling products that have electronic content. During the pandemic in 2020 we’ve seen a surge in sales for bicycles, e-bikes, spin bikes and trainers as people wanted a simple way of getting around town running errands, or… Read More

Conference: Embedded DevOps

The catchy phrase DevOps is defined by Agile advocates as, “The practice of operations and development engineers participating together in the entire service lifecycle, from design through the development process to production support.”

I’ve been developing software since the stone ages, which means… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?