You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Harry Foster and I started in semiconductors at the same time so it was great to reminisce while talking about the latest Wilson Research Group Functional Verification Trend reports. Before I get into the reports lets talk about Harry who is a verification superstar:

Harry is Chief Scientist Verification for the Design Verification… Read More

Based on the Intel investor call yesterday here are some interesting comments Bob Swan made related to Intel outsourcing manufacturing and 7nm progress. Let’s start with the prepared statement:

Bob Swan: “Over the last couple of years, we have been focused on three critical priorities; improving our execution to strengthen … Read More

Hands down, without a doubt, the most interesting CEO in semiconductors is Lip-Bu Tan, founder of Walden Capitol and current CEO of Cadence Design Systems. If you want to talk about a man with a plan it’s Lip-Bu Tan.

Before we get into the fireside chat between Tom Caufield and Lip-Bu at the GTC 2020 Virtual event let’s do a quick biography:… Read More

TSMC is the bellwether for not just the semiconductor industry but the worldwide economy. TSMC makes semiconductors, semiconductors are where electronics begin and electronics are the foundation of modern life, absolutely.

Apple is also a key economic indicator and as we all know Apple is a strategic partner of TSMC. The Apple… Read More

What brought you to semiconductors?

As a kid I was interested in electronics and early personal computers. I went on to graduate from Manchester University in 1986, the birthplace of the modern computer, studying Computer Engineering where for my final year project I designed a gate array using Ferranti Electronics technology… Read More

I am pleased to introduce Truechip to the SemiWiki community. Truechip is a leader in the IP Verification – Design and Verification solutions market, one of the fastest growing market segments we track. Truechip has been serving customers for more than 10 years specialization in VIP integration, customization and SOC Verification.… Read More

First let me tell you that I have nothing but respect for Intel. I grew up with them in Silicon Valley and have experienced firsthand their brilliance and the many contributions they have made to the semiconductor industry. In fact, I can easily say the semiconductor ecosystem would not be what it is today without Intel.

But no company… Read More

Wally Rhines is President and CEO of Cornami, Inc., a company named for its “tsunami of cores”. The company has developed a “TruStream” programming environment that generates independent executable streams of data and control. They have also designed a chip that provides the computational fabric for multi-core execution of… Read More

Virtual events are coming fast and furious. Even though we are sheltering there is still the need to pick and choose carefully because time really is big money inside the semiconductor design ecosystem, absolutely.

Synopsys virtual events are high on my list for three reasons:

- They are very well organized and professionally

…

Read More

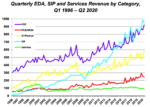

The ESD Alliance tracks revenue growth for a large number of EDA companies. Their recent report paints a positive picture in a landscape dotted with challenges and not-so-good news. The report cites 12.6% overall revenue growth for Q2 2020 vs. Q2 2019. Furthermore, the overall most recent four quarter revenue average has increased… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?