You’ve heard about Meltdown and Spectre and you know they’re really bad security bugs (in different ways). If you’ve dug deeper, you know that these problems are related to the speculative execution common in modern processors, and if you dug deeper still you may have learned that underlying both problems are exploits called timing… Read More

Author: Bernard Murphy

Webinar: Differential Energy Analysis for Improved Performance/Watt in Mobile GPU

May want to listen up; Qualcomm are going to be sharing how they do this. There is a constant battle in designing for low power; you don’t accurately know what the power consumption is going to be until you build it, but by the time you’ve built it, it’s too late to change the design. So you have to find methods to estimate power early on,… Read More

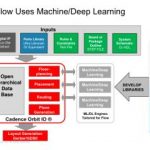

Cadence Selected to Support Major DARPA Program

When DARPA plans programs, they’re known for going big – really big. Which is what they are doing again with their Electronics Resurgence Initiative (ERI). Abstracting from their intro, this is a program “to ensure far-reaching improvements in electronics performance well beyond the limits of traditional scaling”. This isn’t… Read More

Innovation in IoT

There is some interesting work reported this month in the Communications of the ACM, on novel sensing, multi-purpose uses for existing sensors and new ideas in agricultural IoT. The article opens on a method called Hitch-hike to use back-scatter methods for communication; I confess this doesn’t interest me so much, so I won’t … Read More

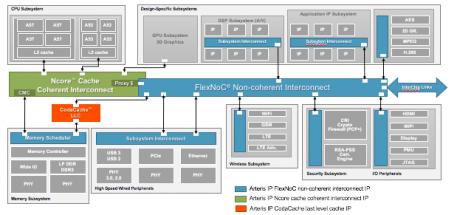

A Last-Level Cache for SoCs

We tend to think of cache primarily as an adjunct to processors to improve performance. Reading and writing main memory (DRAM) is very slow thanks to all the package and board impedance between chips. If you can fetch blocks of contiguous memory from the DRAM to a local on-chip memory, locality of reference in most code ensures much… Read More

Platform ASICs Target Datacenters, AI

There is a well-known progression in the efficiency of different platforms for certain targeted applications such as AI, as measured by performance and performance/Watt. The progression is determined by how much of the application can be run with specialized hardware-assist rather than software, since hardware can be faster… Read More

Deep Learning: Diminishing Returns?

Deep learning (DL) has become the oracle of our age – the universal technology we turn to for answers to almost any hard problem. This is not surprising; its strength in image and speech recognition, language processing and multiple other domains amaze and shock us, to the point that we’re now debating AI singularities. But then,… Read More

Drop-In Security for IoT Edge Devices

You’re excited about the business potential for your cool new baby monitor, geo-fenced kid’s watch, home security system or whatever breakthrough app you want to build. You want to focus on the capabilities of the system, connecting it to the cloud and your marketing rollout plan. Then someone asks whether your system is architected… Read More

CEO Interview: Cristian Amitroaie of AMIQ EDA

AMIQ EDA has caught my attention over the last few months. My first impression was that this was just another small IDE company trying to compete with established and bundled IDEs from the big 3, a seemingly insurmountable barrier. This view was challenged by an impressive list of testimonials, not just from the little guys but also… Read More

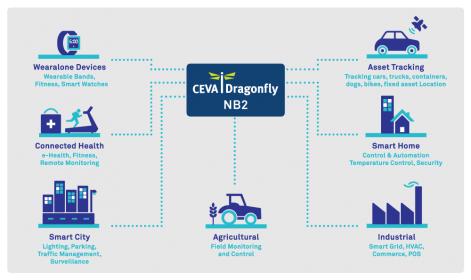

Dragonfly-NB2: You Can Have It All in Your IoT Device

I wrote last month about CEVA’s Dragonfly-NB1 platform, a single-chip IoT solution supporting narrow-band cellular communication; this can meet aggressive total solution price-targets for high-volume deployment, long-range access and the low-power needed for 10+ year battery lifetimes. That solution, based on Release… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior