Mentor just released a white paper on this topic which I confess has taxed my abilities to blog the topic. It’s not that the white paper is not worthy – I’m sure it is. I’m less sure that I’m worthy to blog on such a detailed technical paper. But I’m always up for a challenge, so let’s see what I can make of this, extracting a quick and not very… Read More

Author: Bernard Murphy

SpyGlass Gets its VC

It’s a matter of pride to me and many others from Atrenta days that the brand we built in SpyGlass has been so enduring. It seems that pretty much anyone who thinks of static RTL checking thinks SpyGlass. Even after Synopsys acquired Atrenta, they kept the name as-is, I’m sure because the brand recognition was so valuable.

Even good… Read More

Mentor Masterclass on ML SoC Design

I was scheduled to attend the Mentor tutorial at DVCon this year. Then coronavirus hit, two big sponsors dropped out and the schedule was shortened to three days. Mentor’s tutorial had to be moved to Wednesday and, as luck would have it, I already had commitments on that day. Mentor kindly sent me the slides and audio from the meeting… Read More

5G Infrastructure Opens Up

It seemed we were more or less resigned to Huawei owning 5G infrastructure worldwide. Then questions about security came to the fore, Huawei purchases were put on hold (though that position is being tested outside the US) and opportunity for other infrastructure suppliers (Ericsson, Nokia, etc) has opened up again.

Building … Read More

Innovation in Verification March 2020

This blog is the next in a series in which Paul Cunningham (GM of the Verification Group at Cadence), Jim Hogan and I pick a paper on a novel idea we appreciated and suggest opportunities to further build on that idea.

We welcome comments on our blogs and suggestions for new topics if they’re based on published work.

The Innovation

Our… Read More

An Objective Hardware Security Metric in Sight

Security has been a domain blessed with an abundance of methods to improve in various ways, not so much in methods to measure the effectiveness of those improvements. With the best will in the world, absent an agreed security measurement, all those improvement techniques still add up to “trust me, our baby monitor camera is really… Read More

Trends in AI and Safety for Cars

The potential for AI in cars, whether for driver assistance or full autonomy, has been trumpeted everywhere and continues to grow. Within the car we have vision, radar and ultrasonic sensors to detect obstacles in front, behind and to the side of the car. Outside the car, V2x promises to share real-time information between vehicles… Read More

Hybrid Verification for Deep Sequential Convergence

I’m always curious to learn what might be new in clock domain crossing (CDC) verification, having dabbled in this area in my past. It’s an arcane but important field, the sort of thing that if missed can put you out of business, but otherwise only a limited number of people want to think about it to any depth.

The core issue is something… Read More

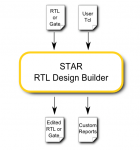

Build Custom SoC Assembly Platforms

I’ve talked with Defacto on and off for several years – Chouki Aktouf (CEO) and Bastien Gratreaux (Marketing). I was in a similar line of business back in Atrenta. Now I’m just enjoying myself, I’ve written a few blogs for them. I’ll confess I wondered why they wouldn’t struggle with the same problems we’d had. Script-driven RTL editing,… Read More

High-Level Synthesis at the Edge

Custom AI acceleration continues to gather steam. In the cloud, Alibaba has launched its own custom accelerator, following Amazon and Google. Facebook is in the game too and Microsoft has a significant stake in Graphcore. Intel/Mobileye have a strong lock on edge AI in cars and wireless infrastructure builders are adding AI capabilities… Read More

Solving the EDA tool fragmentation crisis