This week Cadence introduced Legato™ Reliability Solution, intended to address increased challenges in designing high-reliability analog and mixed-signal ICs for automotive, industrial, aerospace and defense applications.… Read More

Author: Alex Tan

Legato Reliability Solution

TSMC Technologies for IoT and Automotive

At TSMC 2018 Silcon Valley Technology Symposium, Dr Kevin Zhang, TSMC VP of Business Development covered technology updates for IoT platform. The three growth drivers in this segment namely TSMC low power, RF enhancement and embedded memory technology (MRAM/RRAM) reinforced both progress and growth in global semiconductor… Read More

TSMC Technologies for Mobile and HPC

During TSMC 2018 Technology Symposium, Dr. B.J. Woo, TSMC VP of Business Development presented market trends in the area of mobile applications and HPC computing as well as shared TSMC progress in making breakthrough efforts in the technology offerings to serve these two market segments.

Both 5G and AI are taking the center stage… Read More

Cross View Static Validation

Improper handling of design validation could simply translate into a debugging exercise. In mainstream RTL2GDS flow, design implementation involves a top-level integration and lower-level block developments. These lower-level components, comprising of macros, IPs and standard cells are subjected to frequent abstraction… Read More

Virtuoso at CDNLive – A Press Briefing With Yuval Shay

At CDNLive Silicon Valley 2018, I talked with Yuval Shay, Director of Product Management of Cadence Custom IC & PCB Group to scope out some more details on the recent Virtuoso product refresh announced earlier in the morning by Cadence Sr. VP & GM of the same group, Tom Beckley.

Tom shared his view on enabling the fourth industrial… Read More

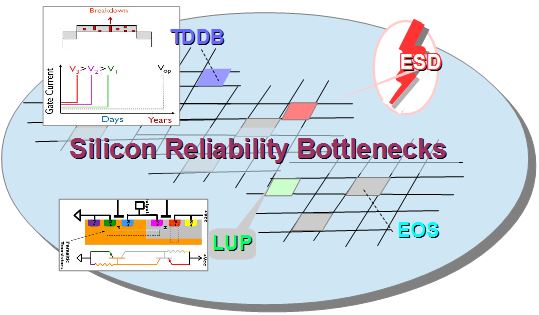

Electrical Reliability Verification – Now At FullChip

Advanced process technology offers both device and interconnect scaling for increased design density and higher performance while invoking also significant implementation complexities. Aside from the performance, power and area (PPA) aspects, designer is getting entrenched with the need of tackling more reliability … Read More

RDC – A Cousin To CDC

In a post-silicon bringup, it is customary to bring the design into a known state prior to applying further testing sequences. This is achieved through a Power-on-Reset (POR) or similar reset strategy which translates to initializing all the storage elements to a known state.

During design implementation, varying degrees of… Read More

Enabling A Data Driven Economy

The theme of this year CDNLive Silicon Valley keynote given by Cadence CEO, Lip-Bu Tan evolves around data and how it drives Cadence to make a transition from System Design Enablement (SDE) to Data Driven Enablement (DDE). Before elaborating further, he noted on some CDNLive conference statistics: 120 sessions, 84% done by users,… Read More

HCM Is More Than Data Management

While tracking Moore’s Law has become a more expensive and difficult endeavor in the HPC design, the mobile SOC design space is also increasingly heterogeneous and complex. Strict safety guidelines such as the ISO-26262 being imposed in the automotive applications further exacerbate the situation.

Looking closer into the … Read More

Embracing Architectural Intent

During DVCon 2018 in San Jose, one topic widely covered was the necessity of describing and capturing intent. Defining our design intent up-front is crucial to the overall success of a design implementation. It is not limited to applying a process level intent, such as the use of verification intent with embedded assertions in … Read More

Things From Intel 10K That Make You Go …. Hmmmm