Company Overview

Achronix Semiconductor Corporation is a fabless semiconductor corporation based in Santa Clara, California, offering high-performance FPGA solutions. Achronix is the only supplier to have both high-performance and high-density standalone FPGAs and embedded FPGA (eFPGA) solutions in high-volume production. Achronix’s FPGA and eFPGA IP offerings are further enhanced by ready-to-use PCIe accelerator cards targeting AI, ML, networking and data center applications. All of Achronix’s products are supported by best-in-class EDA software tools.

Achronix has taken a long, circuitous, and ultimately very successful path to becoming a successful semiconductor device and IP company. This chapter describes the company’s development path from the initial idea to develop the world’s highest-performance FPGA using asynchronous logic to the company’s current role as the only semiconductor company to offer FPGAs as chips, chiplets, and as embedded FPGA IP cores.

While most FPGA companies took root and grew up in Silicon Valley, Achronix did not. Instead, Achronix was founded in Ithaca, New York by John Lofton Holt, a successful business consultant who had worked at Pricewaterhouse Coopers and Booz Allen Hamilton and then later founded his own technology consulting firm. He also became an entrepreneur. Other founders included Dr. Rajit Manohar, a professor of electrical and computer engineering (ECE) at Cornell University who has specialized in asynchronous logic design for more than two decades; Dr. Clinton Kelly, IV, who was one of Dr. Manohar’s PhD students and served as Achronix’s first VP of Advanced Technology while managing most of the company’s hardware engineering team for more than a decade; and Dr. Virantha Ekanayake, who received his PhD at Cornell and then became an Assistant Professor in the ECE Department at Johns Hopkins University where he headed the Asynchronous VLSI and Architecture group before joining Achronix full-time in 2006 as its CTO. These four people constituted Achronix’s entire team for the company’s first two years.

Phase 0: Brainstorming the Company

Holt met Manohar while searching for semiconductor technologies that looked ripe for investment. At the time, very few investors were making hardware/semiconductor investments and Holt believed that there was a gap in the market that could be exploited with the right set of hardware technologies. Manohar was pioneering asynchronous logic circuits at the time. The two became friends. Manohar told Holt about a new, high-performance asynchronous logic chip that his Cornell team had just taped out. Holt and Manohar discussed the business possibilities for fast asynchronous circuits on Holt’s front porch in Ithaca on a hot day in July, 2004. They discussed the benefits of asynchronous logic and technology’s challenges. Holt then spent the next month determining where the technology might be applied to best effect and for the biggest return on investment.

High-end FPGAs had the best margins in the semiconductor business, so Holt decided to attack the FPGA market with Manohar’s asynchronous logic technology. The duopoly at the top of the FPGA pyramid, Altera and Xilinx, were essentially offering identical FPGA products with very similar performance characteristics and Holt’s research suggested that there was a large and untapped market for FPGAs with significantly more performance than the devices offered by the FPGA leaders.

Because of the FPGA’s compelling margins, more than a dozen startup companies had jumped into the FPGA arena along with the four long-established players: the Altera/Xilinx duopoly plus Actel and Lattice. Nearly all of these FPGA startup companies had failed after collectively burning through nearly a billion dollars in startup capital. All of these failed startups offered some combination of unfamiliar silicon and unfamiliar tools, so it was very difficult for them to find customers who would take them seriously against the established players.

Despite the fact that all of these FPGA startups had failed, Holt felt that Manohar’s asynchronous logic technology would give Achronix a clear, competitive advantage over the more established FPGA vendors at

the high-performance end of the product spectrum. Holt’s research suggested that there was a significant market for FPGAs that could deliver more performance than even the high-end FPGAs available from the Altera/Xilinx duopoly. Many prospective FPGA customers seemed willing to pay a premium for that additional performance. But, having “familiar silicon and familiar tools” was going to be essential to be successful.

Phase 1: Creating the Company

Based on Holt’s business analyses, the founders incorporated the company on August 4th, 2004, and immediately set out to build an FPGA that could deliver extremely high performance by leveraging the additional speed made possible by using asynchronous logic. (All other FPGAs were and still are based on synchronous logic.) However, offering devices based on unfamiliar asynchronous logic design methodologies to FPGA users that only knew how to design with synchronous circuits presented a real problem. Worse, the mainstream EDA tools used to develop FPGA-based designs only understood synchronous circuits.

To circumvent these basic market problems, Achronix designed an FPGA that used asynchronous circuits internally to achieve high speeds and then wrapped the asynchronous FPGA core with synchronous circuits. The company also developed specialized design tools to mask the asynchronous nature of the inner FPGA core so that it was not directly visible to FPGA users. Engineers would design systems with Achronix FPGAs using the same, familiar RTL design flow and familiar design tools from leading EDA companies including Mentor Graphics and Synplicity, while reaping the performance benefits of the asynchronous logic in the FPGA core.

Achronix spent the first two years taping out a prototype asynchronous FPGA in 180 nm silicon that achieved 650 Megahertz operation, which was significantly faster than any competing FPGA technology at the time, while simultaneously developing specialized design tools to de-risk the FPGA’s asynchronous logic core. The specialized design tools integrated seamlessly with the leading logic-synthesis tool for FPGAs – Synplicity – which is still the leading FPGA synthesis tool today.

After proving the concept with the 180 nm FPGA device, Achronix taped out a second FPGA in 90 nm technology. Holt recalls that he was shopping in a grocery store in late 2005 when he got a call from Dr. Kelly, who reported that the 90 nm silicon was back from the fab and was running at 1.93 Gigahertz. The target had been 1.5 Gigahertz. Holt remembers scaring most of the people in the grocery store when he let out a huge howl of sheer delight at the news.

Achronix announced this achievement to the world in a press release on April 24, 2006. Even today, in 2019, no commercial FPGA delivers anything close to this performance. For the first time, a startup FPGA company had developed a new and compelling FPGA technology with familiar silicon and familiar tools.

At this point, Achronix had proven asynchronous FPGA technology by delivering 4x to 5x more performance than competing synchronous FPGAs available at the time. Holt packed his bags, left Ithaca, and spent the next year trying to raise venture capital in Silicon Valley. It proved extremely difficult. Two dynamics were in play. One was that VCs (venture capitalists) just were not interested in investing money in chip startups at the time. Worse, it seems that every big VC in the space already had at least one failed or failing FPGA company in their portfolio. These VCs were not looking to add another FPGA startup to their portfolios.

One other factor hampered the raising of venture money: Achronix’s founding team did not fit the standard mold for a Silicon Valley chip startup. The founders were not the typical bunch of Stanford grads who had worked at Nvidia for ten years. They were a group of guys out of Princeton and Cornell University on the East coast.

VCs fully understood the FPGA space. It was a high-margin, high-profit semiconductor business and it was a very interesting space. However, Silicon Valley VCs did not believe that any team, especially not one from the East coast, could deliver. West coast VCs believed that semiconductors were not really a thing back East, so they did not think that a founding team from the East coast could successfully create an FPGA based on asynchronous logic that would outperform FPGAs from the established vendors. Further, they did not think that is was possible to make an asynchronous FPGA look like the familiar, synchronous FPGAs or that an asynchronous FPGA design flow could be fully compatible with the familiar design flows based on the leading EDA tools.

In addition, Holt was all of 29 years old at the time; he simply did not fit the standard mold for a startup semiconductor company’s CEO. For all of these reasons, Holt found it very hard to convince the Silicon Valley VCs to invest in Achronix, so he packed his bags once more, went back East, and quickly landed VCs who were willing to take a chance on an FPGA company based in New York state, partly because they did not yet have failing FPGA companies in their portfolios.

Achronix moved from Ithaca to Silicon Valley in 2006. Holt packed his car with one bag and a computer and arrived in San Jose thirty-nine hours later after an overnight stay in Lincoln, Nebraska. Holt had built many relationships in Silicon Valley and the coast-to-coast move allowed him to attract high-quality talent from other semiconductor and FPGA vendors including Actel, Altera, Lattice, LSI Logic, and Xilinx. (Very few people living in the California climate are willing to move back East, where there is snow and ice for big portions of the year.)

Because Achronix had not yet established a Silicon Valley headquarters, the company met in a rented conference room at Marriott’s Fairfield Inn & Suites on First Street near Norman Y. Mineta San Jose International Airport for the first two weeks. During these early meetings, Holt absorbed hard-earned knowledge about running an FPGA and semiconductor company and about the FPGA market from his new recruits.

It is one thing to make an FPGA; It is quite another to sell them at a profit on the open market against established competitors. In effect, Holt was preparing for battle against larger, more established competitors. However, he was buoyed by the fact that his new employees had left big salaries and substantial financial packages to join his new FPGA startup. He had recruited a team of believers.

Phase Two: Growing the Company

Over the next two years, Achronix focused on getting its first commercial FPGA to market. As a startup, Achronix had to do many things in parallel: build the product, build the team, and develop critical partnerships with EDA vendors including Mentor Graphics and Synplicity. Early on, Holt realized that his fledgling FPGA startup could not afford to have the software-engineering staff needed to develop a full suite of EDA tools for the company’s FPGAs. So, from the start, Achronix relied on existing best-in-class tools from leading EDA vendors, which it would adapt for its FPGAs. Even so, Achronix needed to hire a lot of people. Holt compares the effort to building a car, you are building the factory to manufacture all of the parts for the car, while you are building the assembly line that assembled the cars. Everything needed to happen in parallel.

Achronix also partnered very aggressively on the IP side. It developed close relationships with companies that provided essential IP such as Snowbush Microelectronics. Achronix funded Snowbush’s development of a multi-standard, high-speed SerDes that operated at one to ten Gigabits per second. The company also partnered with True Circuits for other IP cores and worked with ASIC specialist eSilicon. Through these partnerships, Achronix successfully brought its first 65 nm product to market, introducing it as the Speedster FPGA on September 16, 2008. The original Speedster FPGA ran at over 1.5 Gigahertz – significantly faster than any other FPGA on the market, then or now. The design flow that encapsulated the FPGA’s asynchronous core worked so well that engineers could easily use their existing, familiar EDA tools to design with the Achronix FPGAs. Early-access customers successfully pushed designs through the Achronix design flow.

A Serious Miscalculation

However, over the next 12 to 18 months, Achronix discovered that it had seriously underestimated how important power consumption was to FPGA users. Hardware engineers must almost always trade off speed versus power when selecting any electronic technology and a 1.5 Gigahertz FPGA necessarily draws a lot of power.

As a car enthusiast, Holt makes the following analogy. Bugatti’s $3 million Chiron automobile has a 16-cylinder, W-16 engine that develops 1200 horsepower. The car has a top speed of 261 miles per hour (420 kilometers per hour) but it gets four miles to the gallon and drains the gas tank in ten minutes at that speed. Not a lot of people need a street-legal car like that.

Ultimately, Achronix’s asynchronous Speedster FPGA drove several million dollars in revenue. However, it quickly became apparent that Achronix’s initial FPGA offering would not be the product to make the company profitable, which of course was the ultimate objective. Achronix needed to pivot its product strategy.

The company had developed a great team and a phenomenal software design flow. It had also developed a semiconductor sales channel and a great team of nearly 100 people. It had successfully brought an FPGA and development tool suite to market with that small team – something that established FPGA vendors needed thousands of people to achieve.

However, Achronix had essentially misread the market by overemphasizing raw speed over power consumption. The market wanted speed, but not at any cost. Power consumption was still a significant part of the tradeoff equation. Achronix’s development team tried many ways to reduce the power consumption of the asynchronous FPGA technology, but ultimately decided to discontinue the use of asynchronous-logic technology.

The First Pivot: Partnering with Intel

In 2010, Achronix pivoted its strategy to focus on building a synchronous FPGA that leveraged a small bit of the company’s existing asynchronous technology in some internal blocks. The new, synchronous FPGA was still optimized for the high-performance, high-margin, high-end part of the FPGA market, which essentially meant that the key target applications were telecom and networking. The new synchronous FPGA design incorporated a significant amount of hardened IP to maximize performance, but the other prong of the high-performance strategy, that part that would differentiate Achronix from the other FPGA players, was to partner with Intel.

Achronix was the first company to cut a deal with Intel for the manufacture of high-performance ICs based on Intel’s 22 nm, FinFET process. The press release announcing this deal appeared on November 1, 2010 and said:

“The Achronix Speedster®22i FPGA family will shatter existing limitations of FPGAs, allowing cost-effective production of high-performance devices over 2.5M LUTs in size, equivalent to an ASIC of over 20 million gates.”

Partnering with Intel rocketed Achronix into a very high-profile trajectory. With that deal, Achronix leapfrogged its two large FPGA competitors, Altera and Xilinx, which were using a 28-nanometer, planar, CMOS process technology that delivered substantially less performance. Although Achronix had left asynchronous logic behind, the company had found a way to maintain its performance leadership by leveraging Intel’s leading-edge process technology.

Achronix spent the next two years developing the Speedster22i FPGA family. It was a huge design challenge, partly because Intel was not established as a chip foundry. It was not TSMC. Intel’s chip-design tools and design rules were unique to Intel. Although Achronix got a lot of attention and help from Intel as its first foundry customer for the advanced 22 nm, FinFET process, the Speedster22i FPGA took much longer to build and a lot more money than expected. On February 20, 2013, Achronix announced that it had begun shipping the Speedster22i HD1000 FPGA to customers.

The Second Pivot: A New President and CEO

After the Intel partnership announcement, Holt realized that he had been working exclusively on Achronix as CEO for more than six years. It had been a huge investment of his time and of his own money because Holt had invested a big chunk of his personal wealth on the startup. He realized that he needed someone new and fresh to help the company grow faster and to eventually take it public.

Holt had known FPGA industry veteran Robert Blake, another consultant, for several years. He and Blake had become friends and they had an excellent, professional working relationship as well. Eventually, Holt suggested that Blake take over as Achronix’s President and CEO. Holt says that this decision was very, very difficult for him, personally. He’d put his heart and soul into the company for several years and found it very hard to let go of the reins. But, from his time as a management consultant to CEOs, Holt knew that it was the right decision.

Ultimately, Holt did not fully release all of the reins. Holt and Blake enjoyed working together and developed a divide-and-conquer strategy. Blake became President and CEO and Holt became Achronix’s Chairman. The public announcement of the management change came on April 15, 2011. This was an emotional and bittersweet moment for Holt, but he quickly saw that he had made an excellent decision in hiring Blake.

The Third Pivot: Embedded FPGAs and Chiplets

Focusing exclusively on high-performance, high-margin FPGAs limited Achronix’s TAM (total available market). There is a significant market for mid-range and low-end FPGAs and Achronix could not address those markets with the high-performance Speedster22i FPGA. The available margins in those market segments could not support high-end devices made in Intel’s highest-speed process technology, yet these markets are still attractive because of their significantly higher product volumes. Achronix needed a different product strategy to make forays into these lower-tier FPGA markets, which were served by other FPGA vendors.

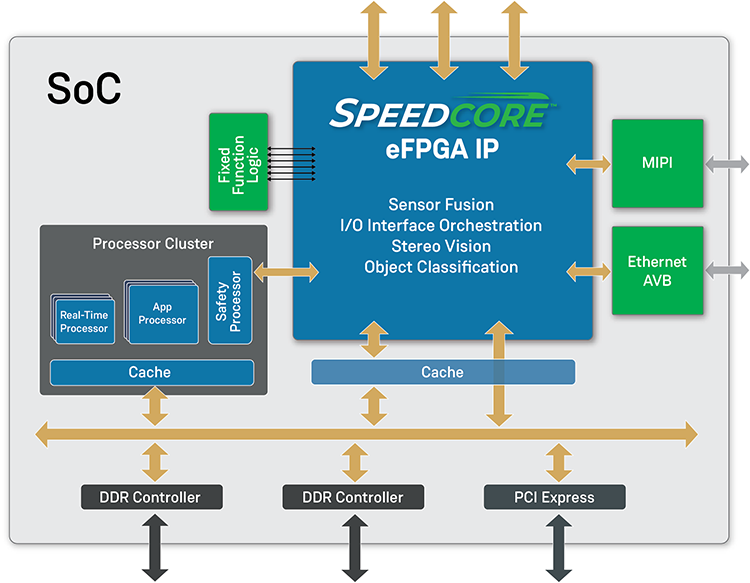

The new strategy developed as a result of the path that Achronix had taken to develop its first-and second-generation FPGAs. Achronix had developed a chip-design flow that treated the FPGA core as a standalone IP core to accommodate the company’s initial strategy of wrapping an asynchronous FPGA core in synchronous peripheral circuitry to make it compatible with existing EDA tools. This design approach—developing the FPGA core as a standalone IP block—was unique in the FPGA industry and it suggested a similar, IP-based product for the lower-tier markets. The new product would be an embedded FPGA or “eFPGA”: an encapsulated design for an FPGA core that could be dropped into any company’s SOC design. Coincidentally, the SOC market was just becoming ready for such a product.

Achronix had been investing in eFPGAs since 2010 but there was a significant problem. An eFPGA core requires a significant amount of silicon real estate compared to most other IP cores, although not nearly as much silicon as a complete FPGA due to many integration efficiencies such as the lack of peripheral I/O circuits capable of driving traces on a circuit board. Achronix had developed an embedded FPGA core for the 28 nm process node, but it was not economically attractive. The 28 nm core needed too much real estate. Early press reaction to Holt’s announcement about these early investments in the eFPGA was skeptical, dismissive, and brutal.

However, at the 16 nm process node, eFPGAs needed much less silicon and were suddenly an economically viable alternative to separately packaged FPGAs. Consequently, Achronix became the first eFPGA IP core supplier, announcing the availability of the first eFPGA cores on October 4, 2012 and instantly created the eFPGA market. Over the next several years, Achronix successfully deployed eFPGAs into some of the largest FPGA customers in the world, allowing them to build their own SOCs with Achronix eFPGA technology, rather than buy expensive and power-hungry FPGA chips from other vendors.

Achronix also jumped on board the relatively recent chiplet trend. The company’s Speedchip product, a high-speed FPGA in chiplet form, is optimized for multi-chip SiP (System in Package) designs. The Speedchip chiplet communicates with a host ASIC or SoC via industry standard, high-speed interconnect such as USR (ultra-short reach) or PCIe XSR (eXtremely short reach) SerDes technology.

Thanks to the introduction of the Speedster22i FPGAs, Speedcore eFPGA IP cores, and Speedchip FPGA chiplets, Achronix crossed over into profitability in Q1, 2017. On June 14, 2017, the company announced a 700-percent increase in year over year revenues and further announced that it expected to cross $100 million in revenue by the end of fiscal 2017, which it did. On February 5, 2019, the EDN Network named Achronix’s Speedcore Gen4 eFPGA IP to its Hot 100 product list for 2018.

At this point, Achronix is the only vendor in the world to offer FPGAs as chips, chiplets, and as IP cores, all served by the same ACE design tool suite.

History and Market Leadership

Achronix is a privately held semiconductor company that was founded in 2004 and has a long history of delivering innovative FPGA products and supporting software tools.

In 2013, Achronix delivered the industry’s most advanced FPGAs with the introduction of Speedster®22i FPGA family with embedded system-level IP for high-performance wireline applications. The Speedster22i family was the first application-specific FPGAs that enabled new, innovative, and high-performance programmable designs. Speedster22i FPGAs have been in high-volume production since 2015.

In 2016, Achronix started shipping Speedcore™ embedded FPGA (eFPGA) IP to some of the largest technology companies in the world. Speedcore IP is the world’s only eFPGA IP solution that is shipping in production in high-volume applications. Speedcore IP is currently available in TSMC 16FF+, TSMC 7nm and TSMC 12FFC technologies. Speedcore IP incorporates the latest technology enhancements such as machine learning processors in addition to customizable amounts of 6-input LUTs, block RAMs along with DSP64 blocks delivering optimized solutions for customer SoC or ASIC solutions.

In 2017, Achronix announced that its revenues grew over 700% year over year and exceeded $100M. Achronix’s exceptional growth was driven primarily by sales of its Speedster22i FPGA family and licensing of its Speedcore embedded FPGA (eFPGA) IP products.

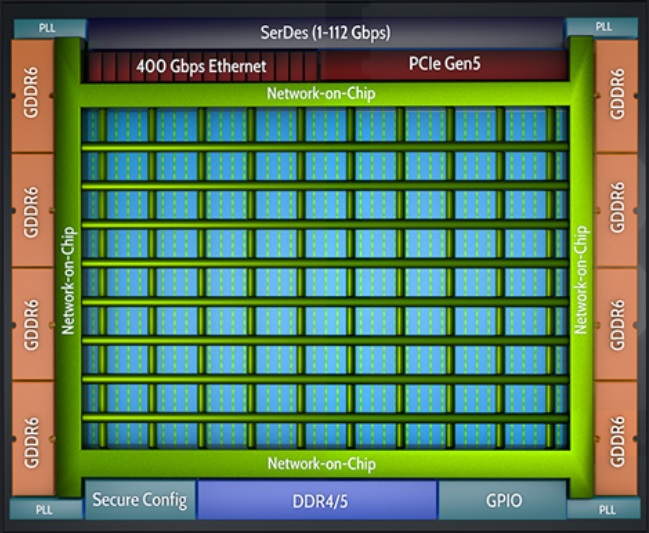

In 2019, Achronix announced the revolutionary Speedster7t FPGA product family based on TSMC 7nm FinFET technology — the first FPGA architecture to offer a 2D network-on-chip (NoC) and an array of machine learning processors optimized for AI/ML workloads.

All of Achronix products are supported by Achronix’s robust and proven ACE design tools — a powerful EDA solution that supports synthesis, place and route, timing closure and debug.

Product Offerings

- Speedster7t FPGAs – Built on TSMC’s 7nm FinFET process, Speedster7t FPGAs feature a revolutionary new 2D network-on-chip (NoC), an array of new machine learning processors (MLPs) optimized for high-bandwidth and artificial intelligence/machine learning (AI/ML) workloads, high-bandwidth GDDR6 interfaces, 400G Ethernet and PCI Express Gen5 ports — all interconnected to deliver ASIC-level performance while retaining the full programmability of FPGAs.

- VectorPath Accelerator Cards – The VectorPath® S7t-VG6 accelerator card is designed to reduce time to market when developing high-performance compute and acceleration functions for artificial intelligence (AI), machine learning (ML), networking and data center applications. The card features Achronix’s high-performance Speedster7t AC7t1500 FPGA fabricated on TSMC’s 7nm FinFET technology.

- Speedcore Embedded FPGAs – The industry’s only silicon-proven, high-density, high-performance eFPGA IP.

Comments

There are no comments yet.

You must register or log in to view/post comments.